# **Datasheet**

# **LG Display**

LP173WF5-SPB4

HD-10-162

The information contained in this document has been carefully researched and is, to the best of our knowledge, accurate. However, we assume no liability for any product failures or damages, immediate or consequential, resulting from the use of the information provided herein. Our products are not intended for use in systems in which failures of product could result in personal injury. All trademarks mentioned herein are property of their respective owners. All specifications are subject to change without notice.

# SPECIFICATION FOR APPROVAL

| ( | ) | Pre | limina | ary Sp | pecification |  |

|---|---|-----|--------|--------|--------------|--|

|   |   |     |        |        |              |  |

(♦) Final Specification

Title

|          |  | ~\.      |                      |  |

|----------|--|----------|----------------------|--|

| Customer |  | SUPPLIER | LG Display Co., Ltd. |  |

| Customer |  |

|----------|--|

| MODEL    |  |

| SOD LILIX | LO Display Co., Ltd. |  |  |

|-----------|----------------------|--|--|

| MODEL     | LP173WF5             |  |  |

| Suffix    | SPB4                 |  |  |

| 7         |                      |  |  |

\*When you obtain standard approval, please use the above model name without suffix

#

Please return 1 copy for your confirmation with your signature and comments.

| APPROVED BY              | SIGNATURE |

|--------------------------|-----------|

| J. Y. Lee / G. Manager   | _         |

| REVIEWED BY              |           |

| I. Y. Jung / Manager [C] |           |

| C. H. Lee / Manager [M]  | _         |

| Y. D. Kim / Manager [P]  |           |

| PREPARED BY              |           |

| J. H. Chae / Engineer    |           |

Products Engineering Dept. LG Display Co., Ltd

Ver. 1.0 Jun. 10, 2019 1 / 29

# **Contents**

| No  | ITEM                                                                                | Page |

|-----|-------------------------------------------------------------------------------------|------|

|     | COVER                                                                               | 1    |

|     | CONTENTS                                                                            | 2    |

|     | RECORD OF REVISIONS                                                                 | 3    |

| 1   | GENERAL DESCRIPTION                                                                 | 4    |

| 2   | ABSOLUTE MAXIMUM RATINGS                                                            | 5    |

| 3   | ELECTRICAL SPECIFICATIONS                                                           | 6    |

| 3-1 | LCD ELECTRICAL CHARACTERISTICS                                                      | 6    |

| 3-2 | LED BACKLIGHT ELECTRICAL CHARACTERISTICS                                            | 7    |

| 3-3 | INTERFACE CONNECTIONS                                                               | 8    |

| 3-4 | eDP SIGNAL TIMING SPECIFICATIONS                                                    | 10   |

| 3-5 | SIGNAL TIMING SPECIFICATIONS                                                        | 14   |

| 3-6 | SIGNAL TIMING WAVEFORMS                                                             | 14   |

| 3-7 | COLOR INPUT DATA REFERENCE                                                          | 15   |

| 3-8 | COLOR INPUT DATA REFERENCE  POWER SEQUENCE                                          | 16   |

| 4   | OPTICAL SPECIFICATIONS                                                              | 17   |

| 5   | MECHANICAL CHARACTERISTICS                                                          | 20   |

| 6   | RELIABLITY                                                                          | 23   |

| 7   | INTERNATIONAL STANDARDS                                                             | 24   |

| 7-1 | SAFETY                                                                              | 24   |

| 7-2 | ENVIRONMENT                                                                         | 24   |

| 8   | PACKING                                                                             | 25   |

| 8-1 | DESIGNATION OF LOT MARK                                                             | 25   |

| 8-2 | PACKING FORM                                                                        | 25   |

| 8-3 | PACKING ASSEMBLY                                                                    | 26   |

| 8-4 | PALLET ASSEMBLY                                                                     | 27   |

| 9   | PRECAUTIONS                                                                         | 28   |

|     | APPENDIX A. LGD PROPOSAL FOR SYSTEM COVER DESIGN                                    | 30   |

|     | APPENDIX B. LGD PROPOSAL FOR eDP INTERFACE DESIGN GUIDE                             | 42   |

|     | APPENDIX C. LGD Proposal for Measurement Method (Thickness / Bracket Height / etc.) | 50   |

|     | APPENDIX D. ENHANCED EXTENDED DISPLAY IDENTIFICATION DATA                           | 51   |

# **Record of Revisions**

| Revision No | Revision Date | Page | Before                                  | After                                | EDID version |

|-------------|---------------|------|-----------------------------------------|--------------------------------------|--------------|

| 0.0         | Apr. 25. 2019 | All  | First Draft (Preliminary Specification) | -                                    | 0.0          |

| 1.0         | Jun. 10. 2019 | 21   | -                                       | Update Mechanical<br>Characteristics | 1.0          |

|             |               | 25   | -                                       | Update Packing                       |              |

|             |               | 50   | -                                       | Update APRENDIX C.                   |              |

|             |               |      |                                         | 201                                  |              |

|             |               |      |                                         |                                      |              |

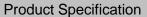

# 1. General Description

The LP173WF5 is a Color Active Matrix Liquid Crystal Display with an integral LED backlight system. The matrix employs a-Si Thin Film Transistor as the active element. It is a transmissive type display operating in the normally Black mode. This TFT-LCD has 17.3 inches diagonally measured active display area with FHD resolution (1920 horizontal by 1080 vertical pixel array). Each pixel is divided into Red, Green and Blue subpixels or dots which are arranged in vertical stripes. Gray scale or the brightness of the sub-pixel color is determined with a 6-bit+FRC gray scale signal for each dot, thus, presenting a palette of more than 16,194,277 colors. The LP173WF5 has been designed to apply the interface method that enables low power, high speed, low EMI. The LP173WF5 is intended to support applications where thin thickness, low power are critical factors and graphic displays are important. In combination with the vertical arrangement of the sub-pixels, the LP173WF5 characteristics provide an excellent flat display for office automation products such as Notebook PC.

### **General Features**

| Active Screen Size  |             | 17.3 inches diagonal                                                   |                        |             |             |  |

|---------------------|-------------|------------------------------------------------------------------------|------------------------|-------------|-------------|--|

| Outline Dimension   | . 0         | 389.89(H, Typ.) × 238.31(V, Typ.) × 3.5(D, Max.) [mm] (with PCB Board) |                        |             |             |  |

| Pixel Pitch         |             | 0.1989 mm X 0.1989 m                                                   | ım                     |             |             |  |

| Pixel Format        | Ť           | 1920 horiz. by 1080 vei                                                | rt. Pixels RGB strip a | rrangement  |             |  |

| Color Depth         |             | 6-bit FRC, 16,194,277                                                  | colors                 |             |             |  |

| Luminance, White    |             | 300 cd/m <sup>2</sup> (Typ.)                                           |                        |             |             |  |

| Power Consumption   | 1           | Total 5.45W (Typ.) Logic: 0.8W (Typ. @ Mosaic), B/L: 4.65W (Typ.)      |                        |             |             |  |

| Weight              |             | 500g (Max.)                                                            |                        |             |             |  |

| Display Operating M | lode        | Normally black                                                         |                        |             |             |  |

| Surface Treatment   |             | Anti-Glare treatment (3H) of the front Polarizer                       |                        |             |             |  |

| RoHS Compliance     |             | Yes                                                                    |                        |             |             |  |

| BFR / PVC / As Free | е           | Yes for all                                                            |                        |             |             |  |

| eDP version(Tcon)   |             | eDP1.2                                                                 |                        |             |             |  |

| DPCD version        |             | Ver1.2                                                                 |                        |             |             |  |

| PSR                 | MBO         | sDRRS                                                                  | SSC                    | NVSR        | G-sync      |  |

| Not support         | Not support | Support                                                                | Support                | Not Support | Not support |  |

Note: Based on system condition(PSR support/PSR none support), Flash Memory data should be changed.

Ver. 1.0 Jun. 10, 2019 4 / 29

# 2. Absolute Maximum Ratings

The following are maximum values which, if exceeded, may cause faulty operation or damage to the unit.

Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                  | Symbol | Val  | ues | Units           | Notes       |  |

|----------------------------|--------|------|-----|-----------------|-------------|--|

| Parameter                  | Symbol | Min  | Max | Units           | Notes       |  |

| Power Input Voltage        | VCC    | -0.3 | 4.0 | V <sub>DC</sub> | at 25 ± 2°C |  |

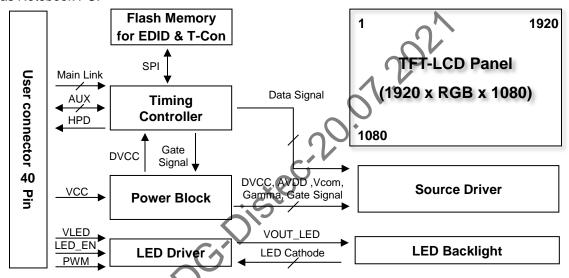

| Operating Temperature      | Тор    | 0    | 50  | °C              | 1           |  |

| Storage Temperature        | Тѕт    | -20  | 60  | O°C             | 1,2         |  |

| Operating Ambient Humidity | Нор    | 10   | 90  | %RH             | 1           |  |

| Storage Humidity           | Нѕт    | 10   | 90  | %RH             | 1,2         |  |

Note: 1. Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be 39°C Max, and no condensation of water.

Note: 2. Storage Condition is guaranteed under packing condition.

**Dry Bulb Temperature [℃]**

# 3. Electrical Specifications

# 3-1. LCD Electrical Characteristics

Table 2. LCD ELECTRICAL CHARACTERISTICS

| Parai                | Symbol     |      | Values | Unit | Notes             |       |   |

|----------------------|------------|------|--------|------|-------------------|-------|---|

| Parai                | Symbol     | Min  | Тур    | Max  | Onit              | Notes |   |

| Power Supply Input   | Voltage    | Vcc  | 3.0    | 3.3  | 3.6               | V     | 1 |

| Permissive Power S   | VCCrp      | -    | -      | 100  | mV <sub>p-p</sub> |       |   |

| Power Supply         | Mosaic     | Icc  | -      | 245  | 305               | mA    |   |

| Input Current        | Red(Solid) | Icc  | -      | 380  | 440               | mA    | 2 |

| Power Consumption    | Pcc        | -    | 0.8    | 1.0  | W                 |       |   |

| Power Supply Inrus   | ICC_P      | - <  | \ · -  | 1.5  | Α                 | 3     |   |

| Differential Impedar | nce        | ZeDP | 90     | 100  | 110               | Ω     |   |

### Note)

- 2. The specified  $I_{CC}$  current and power consumption are under the  $V_{CC}$  = 3.3V , 25 °C, fv = 60Hz condition and Mosaic pattern.

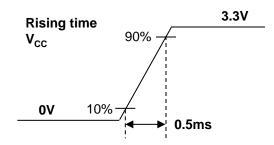

3. The  $\rm V_{\rm CC}$  rising time is same as the minimum of T1 at Power on sequence.

Ver. 1.0 Jun. 10, 2019 6 / 29

# 3-2. LED Backlight Electrical Characteristics

Table 3. LED B/L ELECTRICAL CHARACTERISTICS

| Dama               | Councile of        |                    | Values      |          | Unit | Natas |       |

|--------------------|--------------------|--------------------|-------------|----------|------|-------|-------|

| Para               | meter              | Symbol             | Min         | Тур      | Max  | Unit  | Notes |

| LED Power Input Vo | oltage             | VLED               | 6.0         | 12.0     | 21.0 | V     | 1     |

| LED Power Input Co | urrent             | ILED               | -           | 390      | 400  | mA    | 2     |

| LED Power Consun   | nption             | PLED               | -           | 4.65     | 4.8  | W     | 2     |

| LED Power Inrush ( | Current            | ILED_P             | -           | -        | 1.5  | Α     | 3     |

| PWM Duty Ratio     |                    |                    | 5           | -        | 100  | %     | 4     |

| PWM Resolution     |                    |                    | 10          |          |      | Bit   | 5     |

| PWM Jitter         |                    |                    | 0           | $\sim$ 1 | 0.05 | %     | 6     |

| PWM Frequency      |                    | Fрwм               | 200         | J-7      | 2000 | Hz    | 7     |

|                    | High Level Voltage | V <sub>PWM_H</sub> | 2.5         | \ • -    | 3.6  | V     |       |

| PWM                | Low Level Voltage  | V <sub>PWM_L</sub> | 0 0         | -        | 0.3  | V     |       |

| PVVIVI             | Rising Time        | Tr_pwm             | <i>√O</i> . | -        | 500  | ns    |       |

|                    | Falling Time       | Tf_pwm_            | . / -       | -        | 500  | ns    |       |

| LED EN             | High Voltage       | VLED_EN_N          | 2.5         | -        | 3.6  | V     |       |

| LED_EN             | Low Voltage        | VLED_EN_L          | 0           | -        | 0.3  | V     |       |

| Life Time          |                    |                    | 15,000      | -        | -    | Hrs   | 8     |

### Note)

- 1. The measuring position is the connector of LCM and the test conditions are under 25 °C.

- 2. The current and power consumption with LED Driver are under the  $V_{LED}$  = 12.0V , 25 °C, PWM Duty 100% and White pattern with the normal frame frequency operated(60Hz).

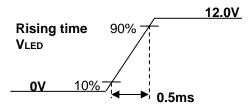

- 3. The  $V_{\text{LED}}$  rising time is same as the minimum of T13 at Power on sequence.

- 4. The operation of LED Driver below minimum dimming ratio may cause flickering or reliability issue.

- 5. 10bit resolution means it's possible to change PWM duty by 0.1% step. (8bit operated by 0.4% step)

- 6. The PWM frequency was selected to avoid for wave noise. Need to check by system side

- 7. This Spec. is not effective at 100% dimming ratio as an exception because it has DC level equivalent to 0Hz. In spite of acceptable range as defined, the PWM Frequency should be fixed and stable for more consistent brightness control at any specific level desired.

- 8. The life time is determined as the time at which brightness of LCD is 50% compare to that of minimum value specified in table 7. under general user condition.

Ver. 1.0 Jun. 10, 2019 7 / 29

# 3-3. Interface Connections

Table 4. MODULE CONNECTOR PIN CONFIGURATION (CN1)

| Pin | Symbol      | Description                          | Notes                                                      |

|-----|-------------|--------------------------------------|------------------------------------------------------------|

| 1   | NC          | No Connection                        |                                                            |

| 2   | GND         | High Speed Ground                    |                                                            |

| 3   | Lane1_N     | Complement Signal Link Lane 1        |                                                            |

| 4   | Lane1_P     | True Signal Link Lane 1              |                                                            |

| 5   | GND         | High Speed Ground                    |                                                            |

| 6   | Lane0_N     | Complement Signal Link Lane 0        |                                                            |

| 7   | Lane0_P     | True Signal Link Lane 0              |                                                            |

| 8   | GND         | High Speed Ground                    |                                                            |

| 9   | AUX_CH_P    | True Signal Auxiliary Channel        | [Connector]                                                |

| 10  | AUX_CH_N    | Complement Signal Auxiliary Channel  | LSC, GT05Q-30S-H10-MN<br>(30pin, 0.5pitch) or equivalent   |

| 11  | GND         | High Speed Ground                    | (Sopin, c.spiton) or equivalent                            |

| 12  | VCC         | LCD logic and driver power           |                                                            |

| 13  | VCC         | LCD logic and driver power           | [Connector pin arrangement]                                |

| 14  | NC          | No Connection                        | Pin 30 Pin 1                                               |

| 15  | GND         | LCD logic and driver ground          |                                                            |

| 16  | GND         | LCD logic and driver ground          |                                                            |

| 17  | HPD         | HPD signal pin                       |                                                            |

| 18  | BL_GND      | LED Backlight ground                 | _                                                          |

| 19  | BL_GND      | LED Backlight ground                 |                                                            |

| 20  | BL_GND      | LED Backlight ground                 |                                                            |

| 21  | BL_GND      | LED Backlight ground                 | [LGD P-Vcom using information] 1. Pin for P-Vcom: #24, #25 |

| 22  | BL ENABLE   | LED Backlight control on/off control | 2. P-Vcom Address : 0101000x                               |

| 23  | BL PWM      | System PWM signal input for dimming  |                                                            |

| 24  | NC Reserved | Reserved for LCD manufacture's use   |                                                            |

| 25  | NC Reserved | Reserved for LCD manufacture's use   |                                                            |

| 26  | VLED        | LED Backlight power (12V Typical)    |                                                            |

| 27  | VLED        | LED Backlight power (12V Typical)    |                                                            |

| 28  | VLED        | LED Backlight power (12V Typical)    |                                                            |

| 29  | VLED        | LED Backlight power (12V Typical)    |                                                            |

| 30  | NC          | No Connection                        |                                                            |

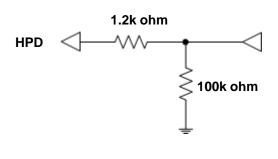

# 3-3-1. Input/output signal circuit

Figure 1. HPD Output circuit is as below

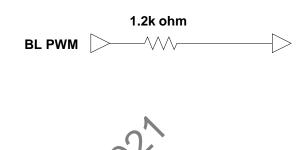

Figure 2. BL PWM input circuit is as below

Figure 3. BL Enable input circuit is as below

Figure 4. BIST input circuit is as below

Ver. 1.0 Jun. 10, 2019 9/29

# 3-4. eDP Signal Timing Specifications

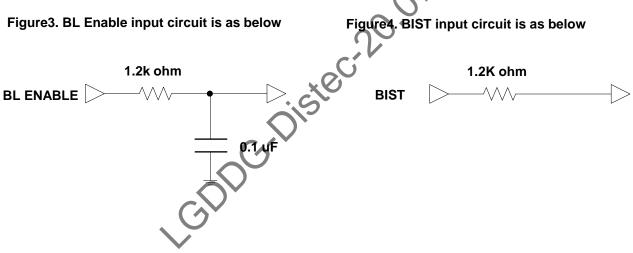

# 3-4-1. Definition of Differential Voltage

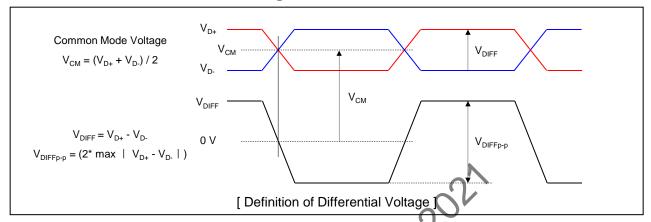

# 3-4-2. Main Link EYE Diagram

[ EYE Mask at Source Connector Pins ]

| Daint | Reduce   | d Bit Rate | High Bit Rate |            |  |  |

|-------|----------|------------|---------------|------------|--|--|

| Point | Time(UI) | Voltage(V) | Time(UI)      | Voltage(V) |  |  |

| 1     | 0.127    | 0.000      | 0.210         | 0.000      |  |  |

| 2     | 0.291    | 0.160      | 0.355         | 0.140      |  |  |

| 3     | 0.500    | 0.200      | 0.500         | 0.175      |  |  |

| 4     | 0.709    | 0.200      | 0.645         | 0.175      |  |  |

| 5     | 0.873    | 0.000      | 0.790         | 0.000      |  |  |

| 6     | 0.709    | -0.200     | 0.645         | -0.175     |  |  |

| 7     | 0.500    | -0.200     | 0.500         | -0.175     |  |  |

| 8     | 0.291    | -0.160     | 0.355         | -0.140     |  |  |

[ EYE Mask Vertices at Source Connector Pins ]

| 20    | 0   |     |     |     | 2         |     |     |     |     |     |

|-------|-----|-----|-----|-----|-----------|-----|-----|-----|-----|-----|

| /olts |     | 1   |     |     |           |     |     | 3   |     |     |

|       |     |     |     |     | <u></u>   |     |     |     |     |     |

| 0.0   | 0.1 | 0.2 | 0.3 | 0.4 | 0.5<br>UI | 0.6 | 0.7 | 0.8 | 0.9 | 1.0 |

[ EYE Mask at Sink Connector Pins ]

| Doint | Reduce   | d Bit Rate | High Bit Rate |            |  |  |  |

|-------|----------|------------|---------------|------------|--|--|--|

| Point | Time(UI) | Voltage(V) | Time(UI)      | Voltage(V) |  |  |  |

| 1     | 0.375    | 0.000      | 0.246         | 0.000      |  |  |  |

| 2     | 0.500    | 0.023      | 0.500         | 0.075      |  |  |  |

| 3     | 0.625    | 0.000      | 0.755         | 0.000      |  |  |  |

| 4     | 0.500    | -0.023     | 0.500         | -0.075     |  |  |  |

[ EYE Mask Vertices at Sink Connector Pins ]

| Point | Reduce   | d Bit Rate | High Bit Rate |            |  |  |  |

|-------|----------|------------|---------------|------------|--|--|--|

| Point | Time(UI) | Voltage(V) | Time(UI)      | Voltage(V) |  |  |  |

| 1     | 0.270    | 0.000      | 0.246         | 0.000      |  |  |  |

| 2     | 0.500    | 0.068      | 0.500         | 0.075      |  |  |  |

| 3     | 0.731    | 0.000      | 0.755         | 0.000      |  |  |  |

| 4     | 0.500    | -0.068     | 0.500         | -0.075     |  |  |  |

[ EYE Mask Vertices at embedded DP Sink Connector Pins ]

Ver. 1.0 Jun. 10, 2019 10 / 29

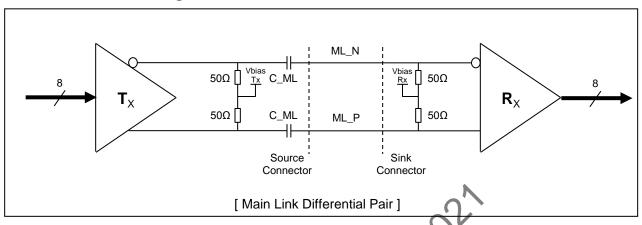

# 3-4-3. eDP Main Link Signal

| Parameter                                            | Symbol                   | Min  | Тур | Max | Unit | Notes             |

|------------------------------------------------------|--------------------------|------|-----|-----|------|-------------------|

| Unit Interval for high bit rate (2.7Gbps / lane)     | UI_HBR                   | -    | 370 | 2,  | ps   |                   |

| Unit Interval for reduced bit rate (1.62Gbps / lane) | UI_RBR                   |      | 617 | -   | ps   |                   |

| Link Clock Down Spreading                            | Amplitude                | 0    |     | 0.5 | %    |                   |

| Link Clock Down Spreading                            | Frequency                | 30   |     | 33  | kHz  |                   |

| Differential peak-to-peak voltage                    | VC                       | 350  | •   | -   | mV   | For HBR(2.7Gbps)  |

| at Source side connector                             | VTX-DIFFp-p              | 400  | 1   | -   | IIIV | For RBR(1.62Gbps) |

| EYE width                                            | $\searrow$               | 0.58 | -   | -   | UI   | For HBR(2.7Gbps)  |

| at Source side connector                             | TX-EYE-CONN              | 0.75 | -   | -   | UI   | For RBR(1.62Gbps) |

| Differential peak-to-peak voltage                    | W                        | 150  | -   | -   | m\/  | For HBR(2.7Gbps)  |

| at Sink side connector                               | V <sub>RX-DIFFp-p</sub>  | 136  | -   | -   | mV   | For RBR(1.62Gbps) |

| EYE width                                            | _                        | 0.51 | -   | -   | UI   | For HBR(2.7Gbps)  |

| at Sink side connector                               | T <sub>RX-EYE-CONN</sub> | 0.46 | -   | -   | UI   | For RBR(1.62Gbps) |

| Rx DC common mode voltage                            | V <sub>RX CM</sub>       | 0    | -   | 1.0 | V    |                   |

| AC Coupling Capacitor                                | C <sub>SOURCE</sub> ML   | 75   |     | 200 | nF   | Source side       |

- 1. Termination resistor is typically integrated into the transmitter and receiver implementations.

- 2. AC Coupling Capacitor is not placed at the sink side.

- 3. In cabled embedded system, it is recommended the system designer ensure that EYE width and voltage are met at the sink side connector pins.

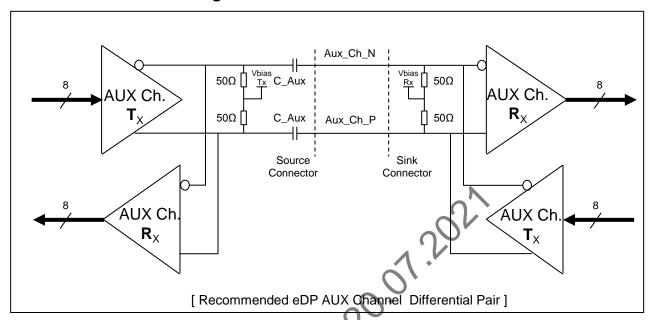

# 3-4-4. eDP AUX Channel Signal

| Parameter                                                  | Symbol                   | Min  | Тур | Max  | Unit | Notes         |

|------------------------------------------------------------|--------------------------|------|-----|------|------|---------------|

| AUX Unit Interval                                          | UI . C                   | 0.4  | -   | 0.6  | us   |               |

| AUX Jitter at Tx IC Package Pins                           | TO/2                     | -    | -   | 0.04 | UI   | Equal to 24ns |

| AUX Jitter at Rx IC Package Pins                           | l jitter                 | -    | -   | 0.05 | UI   | Equal to 30ns |

| AUX Peak-to-peak voltage at Connector Pins of Receiving    |                          | 0.39 | -   | 1.38 | V    |               |

| AUX Peak-to-peak voltage at Connector Pins of Transmitting | V <sub>AUX-DIFFp-p</sub> | 0.36 | -   | 1.36 | V    |               |

| AUX EYE width at Connector Pins of Tx and Rx               |                          | 0.98 | -   | -    | UI   |               |

| AUX DC common mode voltage                                 | V <sub>AUX-CM</sub>      | 0    | -   | 1.0  | V    |               |

| AUX AC Coupling Capacitor                                  | C <sub>SOURCE-AUX</sub>  | 75   |     | 200  | nF   | Source side   |

- 1. Termination resistor is typically integrated into the transmitter and receiver implementations.

- 2. AC Coupling Capacitor is not placed at the sink side.

- 3.  $V_{AUX-DIFFp-p} = 2^* \mid V_{AUXP} V_{AUXN} \mid$

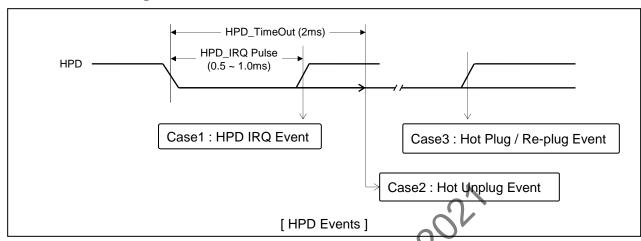

# 3-4-5. eDP HPD Signal

|                                |         |      |            | 4 / |      |                       |

|--------------------------------|---------|------|------------|-----|------|-----------------------|

| Parameter                      | Symbol  | Min  | Тур        | Max | Unit | Notes                 |

| HPD Voltage                    |         | 2.25 |            | 3.6 | V    | Sink side Driving     |

| Hot Plug Detection Threshold   | HPD     | 2.0  | 7          | -   | V    | Course side Detection |

| Hot Unplug Detection Threshold |         | -00  | <b>j</b> - | 0.8 | V    | Source side Detecting |

| HPD_IRQ Pulse Width            | HPD_IRQ | 0.5  | -          | 1.0 | ms   |                       |

| HPD_TimeOut                    |         | 2.0  | -          | -   | ms   | HPD Unplug Event      |

- 1. HPD IRQ : Sink device wants to notify the Source device that Sink's status has changed so it toggles HPD line, forcing the Source device to read its Link / Sink Receiver DPCD field via the AUX-CH

- 2. HPD Unplug: The Sink device is no longer attached to the Source device and the Source device may then disable its Main Link as a power saving mode.

- 3. Plug / Re-plug: The Sink device is now attached to the Source device, forcing the Source device to read its Receiver capabilities and Link / Sink status Receiver DPCD fields via the AUX-CH

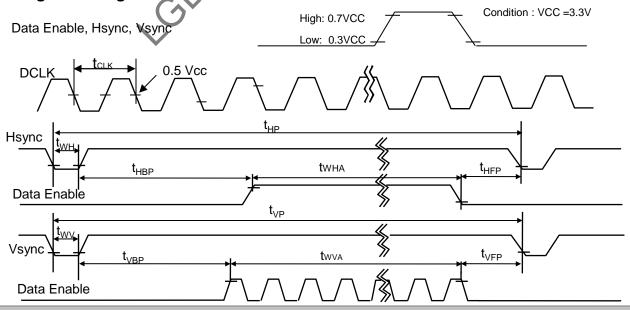

# 3-5. Signal Timing Specifications

This is the signal timing required at the input of the User connector. All of the interface signal timing should be satisfied with the following specifications and specifications of eDP Tx/Rx for its proper operation.

**ITEM Symbol** Min Unit Note Тур Max **DCLK** 138.7 Frequency MHz  $f_{CLK}$ Period 2072 2080 2088 t<sub>HP</sub> 32 32 32 Hsync Width  $t_{WH}$  $t_{CLK}$ Width-Active 1920  $t_{WHA}$ Period 1108 1111  $t_{VP}$ Vsync Width 5 5  $t_{wv}$  $t_{HP}$ 1080 Width-Active  $t_{WVA}$ 80 Horizontal back porch 72 88  $t_{HBP}$  $t_{CLK}$ Horizontal front porch 48 48 Data  $t_{HFP}$ Enable 23 24 Vertical back porch  $t_{VBP}$  $t_{HP}$ 5 3 Vertical front porch  $t_{VEP}$

**Table 4. TIMING TABLE**

**Notice.** all reliabilities are specified for timing specification based on refresh rate of 60Hz. However, LP173WF5 has a good actual performance even at lower refresh rate (e.g. 40Hz or 50Hz) for power saving Mode, whereas LP173WF5 is secured only for function under lower refresh rate. 60Hz at Normal mode, 50Hz, 40Hz at Power save mode. Don't care Flicker level (Power save mode).

# 3-7. Color Input Data Reference

The brightness of each primary color (red, green and blue) is based on the 8-bit gray scale data input for the color; the higher the binary input, the brighter the color. The table below provides a reference for color versus data input.

Table 5. COLOR DATA REFERENCE

|       |             |    |    |    |    |    |    |      |   |    | ı   | npı | ıt Co | olor | Dat | a    |      |   |    |    |    |    |    |    |

|-------|-------------|----|----|----|----|----|----|------|---|----|-----|-----|-------|------|-----|------|------|---|----|----|----|----|----|----|

|       | color       |    |    |    | RE | Đ  |    |      |   |    |     |     | GRE   | EN   |     |      |      |   |    | BL | UE |    |    |    |

|       | .0.01       | MS |    |    |    |    |    | LS   |   | MS |     |     |       |      |     | LSE  |      |   |    |    |    |    |    | SB |

|       |             | R7 | R6 | R5 | R4 | R3 | R2 | R1 F | _ |    |     |     |       |      |     | G1 G | lack |   | B5 | B4 | В3 | B2 | B1 | В0 |

|       | Black       | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0    | _    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | Red         | 1  | 1  | 1  | 1  | 1  | 1  | 1    | 1 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | Green       | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 1  | 1   | 1   | 1     | 11   | ,1  | 1 '  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| Basic | Blue        | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | ō    | 0   | 0 (  | 1    | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| Color | Cyan        | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 1  | 1 ( | 1   | 4     | 1    | 1   | 1 '  | 1    | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|       | Magenta     | 1  | 1  | 1  | 1  | 1  | 1  | 1    | 1 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 1    | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|       | Yellow      | 1  | 1  | 1  | 1  | 1  | 1  | 1    | 1 | C  | 1   | 1   | 1     | 1    | 1   | 1 '  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | White       | 1  | 1  | 1  | 1  | 1  | 1  | 1×   | Y | 1  | 1   | 1   | 1     | 1    | 1   | 1 '  | 1    | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

|       | RED (0)     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | RED (1)     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 1 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| RED   |             |    |    |    |    | 2  |    |      |   |    |     |     |       |      |     |      |      |   |    |    |    |    |    |    |

|       | RED (254)   | 1  | 1  | 1  | 1  | 1  | 1  | 1    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | RED (255)   | 1  | -1 | 1  | 1  | 1  | 1  | 1    | 1 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | GREEN (0)   | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | GREEN (1)   | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0    | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| GREEN |             |    |    |    |    |    |    |      |   |    |     |     |       |      |     |      |      |   |    |    |    |    |    |    |

|       | GREEN (254) | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 1  | 1   | 1   | 1     | 1    | 1   | 1 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | GREEN (255) | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 1  | 1   | 1   | 1     | 1    | 1   | 1 .  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | BLUE (0)    | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|       | BLUE (1)    | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 0    | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

| BLUE  |             |    |    |    |    |    |    |      |   |    |     |     |       | -    |     |      |      |   |    |    |    |    |    |    |

|       | BLUE (254)  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | ) 1  | 1 | 1  | 1  | 1  | 1  | 1  | 0  |

|       | BLUE (255)  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 | 0  | 0   | 0   | 0     | 0    | 0   | 0 (  | 1    | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

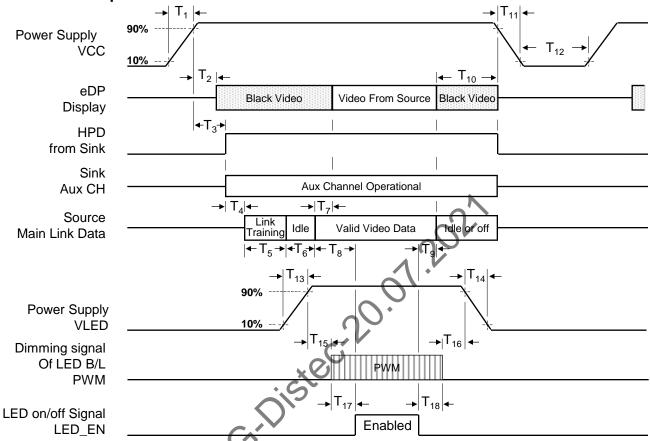

# 3-8. Power Sequence

Table 6 POWER SEQUENCE TABLE

| Cumbal         | Required | Lir | Limits |       | Notes |

|----------------|----------|-----|--------|-------|-------|

| Symbol         | Ву       | Min | Max    | Units | Notes |

| T <sub>1</sub> | Source   | 0.5 | 10     | ms    | -     |

| T <sub>2</sub> | Sink     | 0   | 200    | ms    | -     |

| T <sub>3</sub> | Sink     | 0   | 200    | ms    | -     |

| T <sub>4</sub> | Source   | -   | -      | ms    | -     |

| T <sub>5</sub> | Source   | -   | -      | ms    | -     |

| T <sub>6</sub> | Source   | -   | -      | ms    | -     |

| T <sub>7</sub> | Sink     | 0   | 50     | ms    | -     |

| T <sub>8</sub> | Source   | -   | -      | ms    | 5     |

| T <sub>9</sub> | Source   | -   | -      | ms    | 6     |

| Symbol          | Required | Lir | nits | Units | Notes |

|-----------------|----------|-----|------|-------|-------|

| Syllibol        | Ву       | Min | Max  | Units | Notes |

| T <sub>10</sub> | Source   | 0   | 500  | ms    | -     |

| T <sub>11</sub> | Source   | -   | 10   | ms    | -     |

| T <sub>12</sub> | Source   | 500 | -    | ms    |       |

| T <sub>13</sub> | Source   | 0.5 | 10   | ms    | -     |

| T <sub>14</sub> | Source   | 0.5 | 10   | ms    | -     |

| T <sub>15</sub> | Source   | 10  | -    | ms    | -     |

| T <sub>16</sub> | Source   | 10  | -    | ms    | -     |

| T <sub>17</sub> | Source   | 0   | -    | ms    | -     |

| T <sub>18</sub> | Source   | 0   | -    | ms    | -     |

Note) 1. Do not insert the mating cable when system turn on.

- 2. Valid Data have to meet "3-3. eDP Signal Timing Specifications"

- 3. Video Signal, LED\_EN and PWM need to be on pull-down condition on invalid status.

- 4. LGD recommend the rising sequence of VLED after the Vcc and valid status of Video Signal turn on.

- 5. Driving signal of B/L must be "On" after normal video signal (Normal operating data from source) input.

- 6. B/L driving must be "Off" before normal signal (Normal operating data from source) finish.

# 4. Optical Specification

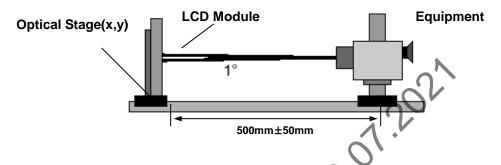

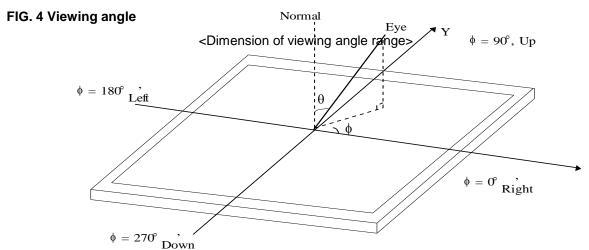

Optical characteristics are determined after the unit has been 'ON' and stable for approximately 20 minutes in a dark environment at 25°C. The values specified are at an approximate distance 50cm from the LCD surface at a viewing angle of  $\Phi$  and  $\Theta$  equal to  $0^{\circ}$ .

FIG. 1 presents additional information concerning the measurement equipment and method.

FIG. 1 Optical Characteristic Measurement Equipment and Method

Table 7. OPTICAL CHARACTERISTICS

Ta=25°C, VCC=3.3V, fv=60Hz

|                       |                       | O ls . s l              | ×0      | Values |                   | l losito          | Natas |  |

|-----------------------|-----------------------|-------------------------|---------|--------|-------------------|-------------------|-------|--|

| P                     | arameter              | Symbol                  | Min     | Тур    | Max               | Units             | Notes |  |

| Contrast Ratio        |                       | CR                      | 600     | 800    | -                 |                   | 1     |  |

| Surface Lumina        | ance, white           | Lwh                     | 255     | 300    | -                 | cd/m <sup>2</sup> | 2     |  |

| Luminance Var         | iation                | δ <sub>WHITE (5P)</sub> | -       | 1.2    | 1.4               |                   | 3     |  |

| Lummance var          | lation                | 8 WHITE(13P)            | -       | 1.4    | 1.6               | -                 | 3     |  |

| Response Time         |                       | Tr + Tf                 | -       | 16     | 25                | ms                | 4     |  |

|                       | RED                   | Rx                      |         | 0.640  |                   |                   |       |  |

|                       | KED V                 | Ry                      |         | 0.330  | Typical<br>+ 0.03 |                   | 5     |  |

|                       | GREEN                 | Gx                      |         | 0.305  |                   |                   |       |  |

| Color                 |                       | Gy                      | Typical | 0.605  |                   |                   |       |  |

| Coordinates           | DLUE                  | Вх                      | - 0.03  | 0.150  |                   |                   | 5     |  |

|                       | BLUE                  | Ву                      |         | 0.055  |                   |                   |       |  |

|                       | VAZI IITE             | Wx                      |         | 0.313  |                   |                   |       |  |

|                       | WHITE                 | Wy                      |         | 0.329  |                   |                   |       |  |

|                       | x axis, right(Φ=0°)   | Θr                      | 80      | -      | -                 |                   |       |  |

| Viewing Angle         | x axis, left (Φ=180°) | ΘΙ                      | 80      | -      | -                 | <b>D</b>          | 0     |  |

|                       | y axis, up (Φ=90°)    |                         | 80      | -      | -                 | Degree            | 6     |  |

| y axis, down (Φ=270°) |                       | Θd                      | 80      | -      | -                 |                   |       |  |

| Gray Scale            |                       |                         |         |        |                   |                   | 7     |  |

Ver. 1.0 Jun. 10, 2019 17 / 29

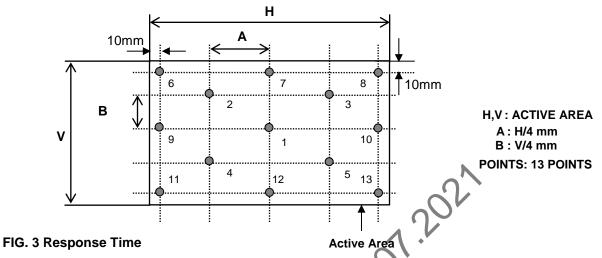

### Note)

1. It should be measured in the center of screen(1 Point). Contrast Ratio(CR) is defined mathematically as

2. Surface luminance is the average of 5 point across the LCD surface 50cm from the surface with all pixels displaying white. For more information see FIG 2.

$$L_{WH}$$

= Average(1,2, ... 5 Point)

3. The variation in surface luminance, The panel total variation (δ WHITE) is determined by measuring N at each test position 1 through 13 and then defined as following numerical formula. For more information see FIG 2.

$$\delta \text{ WHITE (5P)} = \frac{\text{Maximum (1,2, ... 5 Point)}}{\text{Minimum (1,2, ... 5 Point)}} \delta \text{ WHITE (13P)} = \frac{\text{Maximum (1,2, ... 13 Point)}}{\text{Minimum (1,2, ... 13 Point)}}$$

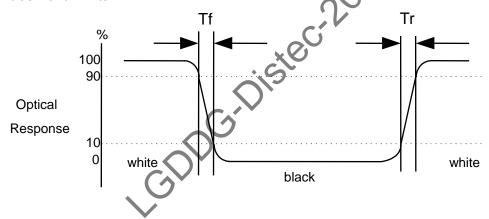

- 4. Response time is the time required for the display to transition from black to white (rise time, Tr) and from white to black (falling time, Tf). For additional information see FIG 3.

- 5. It should be measured in the center of screen (1Point).

- 6. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG 4.

- 7. Gray scale specification

| Gray Level | Luminance [%] (Typ) |

|------------|---------------------|

| LO         | 0.1                 |

| L7         | 0.5                 |

| L15        | 2.8                 |

| L23        | 8.4                 |

| L31        | 18.5                |

| L39        | 33.2                |

| L47        | 51.4                |

| L55        | 70.9                |

| L63        | 100                 |

Ver. 1.0 Jun. 10, 2019 18 / 29

### FIG. 2 Luminance

<Measuring point for Average Luminance & measuring point for Luminance variation>

The response time is defined as the following figure and shall be measured by switching the input signal for "black" and "white".

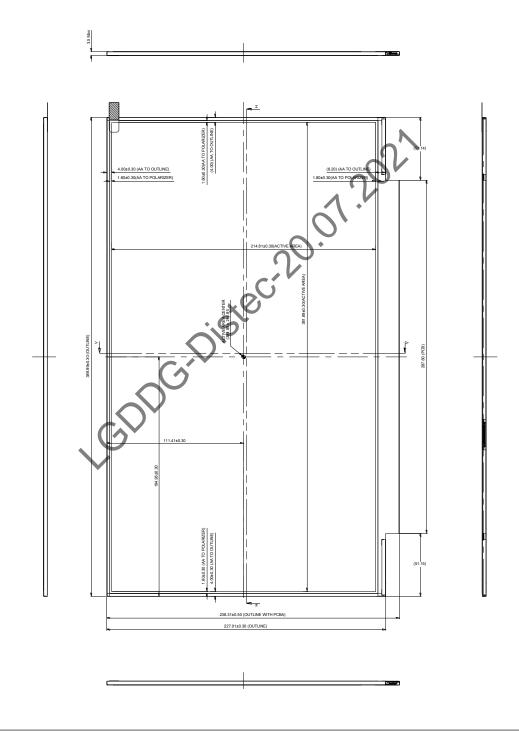

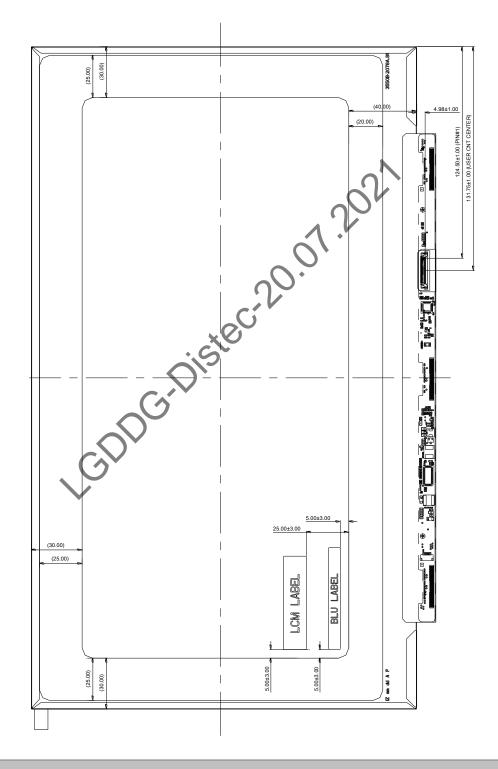

### 5. Mechanical Characteristics

The contents provide general mechanical characteristics for the model LP173WF5. In addition the figures in the next page are detailed mechanical drawing of the LCD.

|                     | Horizontal  | 389.89 ± 0.3 mm                     |  |  |  |  |  |  |

|---------------------|-------------|-------------------------------------|--|--|--|--|--|--|

| Outline Dimension   | Vertical    | 238.31 ± 0.5 mm<br>(with PCB Board) |  |  |  |  |  |  |

|                     | Thickness   | 3.5 mm (Max.)                       |  |  |  |  |  |  |

| Upper Polarizer     | Horizontal  | 385.09 ± 0.3 mm                     |  |  |  |  |  |  |

| Dimension           | Vertical    | 218.21 ± 0.3 mm                     |  |  |  |  |  |  |

| Active Display Area | Horizontal  | 381 89 mm                           |  |  |  |  |  |  |

| Active Display Area | Vertical    | 214.81 mm                           |  |  |  |  |  |  |

| Weight              | 500g (Max.) |                                     |  |  |  |  |  |  |

| Surface Treatment   |             |                                     |  |  |  |  |  |  |

| GDDG:DisteC'        |             |                                     |  |  |  |  |  |  |

<FRONT VIEW>

Notes (Measurement method refer to the Appendix D)

- 1) Unit[mm], General tolerance : ± 0.5mm

- 2) All components except cover shield of LCM is under upper POL.

<REAR VIEW>

- 1) Unit[mm], General tolerance :  $\pm$  0.5mm

- 2) LCM Label Information refer to the page 25.

# 6. Reliability

### Environment test condition

| No. | Test Item                             | Conditions                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | High temperature storage test         | Ta= 60°C, 240h                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | Low temperature storage test          | Ta= -20°C, 240h                                                                                                                                                                                                                                                                                                                                                                          |

| 3   | High temperature operation test       | Ta= 50°C, 50%RH, 240h                                                                                                                                                                                                                                                                                                                                                                    |

| 4   | Low temperature operation test        | Ta= 0°C, 240h                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | Vibration test (non-operating)        | Random, 1.0Grms, 10 ~ 300Hz(PSD 0.0035)<br>3 axis, 30min/axis                                                                                                                                                                                                                                                                                                                            |

| 6   | Shock test (non-operating)            | - No functional or cosmetic defects following a shock to all 6 sides delivering at least 180 G in a half sine pulse no longer than 2 ms to the display module - No functional defects following a shock delivering at least 200 g in a half sine pulse no longer than 2 ms to each of 6 sides. Each of the 6 sides will be shock tested with one each display, for a total of 6 displays |

| 7   | Altitude operating storage / shipment | 0 ~ 10,000 feet (3,048m) 24Hr<br>0 ~ 40,000 feet (12,192m) 24Hr                                                                                                                                                                                                                                                                                                                          |

| 8   | ESD                                   | <ul><li>± 8kV for contact discharge</li><li>± 15kV for air discharge</li></ul>                                                                                                                                                                                                                                                                                                           |

# [ Result Evaluation Criteria ]

- 1. Comparing the initial functional FOS status, there should be no major change which might affect the practical display function when the display reliability test is conducted.

- 2. After conduct reliability tests, LGD guarantees only functional FOS quality.

- 3. In the Reliability Test, Confirm performance after leaving in room temp.

- 4. In the standard condition, there shall be no practical problems that may affect the display function 24 hours later after reliability test. After the reliability test, we can guarantee the product only when the corrosion is causing its malfunction. The corrosion causing no functional defect can not be guaranteed.

Ver. 1.0 Jun. 10, 2019 23 / 29

### 7. International Standards

# 7-1. Safety

- a) UL 60950-1, Underwriters Laboratories Inc.

Information Technology Equipment Safety Part 1 : General Requirements.

- b) CAN/CSA-C22.2 No. 60950-1-07, Canadian Standards Association. Information Technology Equipment - Safety - Part 1 : General Requirements.

- c) EN 60950-1, European Committee for Electro technical Standardization (CENELEC). Information Technology Equipment Safety Part 1 : General Requirements.

- d) IEC 60950-1, The International Electro technical Commission (IEC).

Information Technology Equipment Safety Part 1 : General Requirements

### 7-2. Environment

a) RoHS, Directive 2011/65/EU of the European Parliament and of the council of 8 June 2011

# 8. Packing

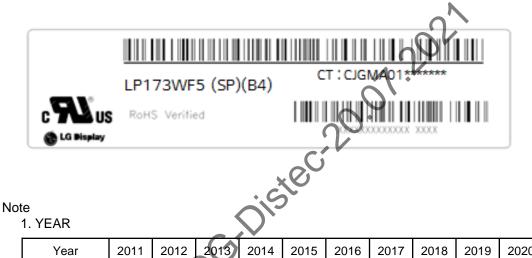

# 8-1. Designation of Lot Mark

a) Lot Mark

A,B,C: SIZE(INCH) D: YEAR

E: MONTH F~ M: SERIAL NO.

### Note

### 1. YEAR

| ı |      |      |      |      |      |      |      |      |      |      |      |

|---|------|------|------|------|------|------|------|------|------|------|------|

| 1 | Year | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

|   | Mark | Α    | В    | ၁    | D    | Е    | F    | G    | Н    | J    | K    |

### 2. MONTH

| Month | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug | Sep | Oct | Nov | Dec |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Mark  | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | Α   | В   | С   |

b) Location of Lot Mark

Serial No. is printed on the label. The label is attached to the backside of the LCD module. This is subject to change without prior notice.

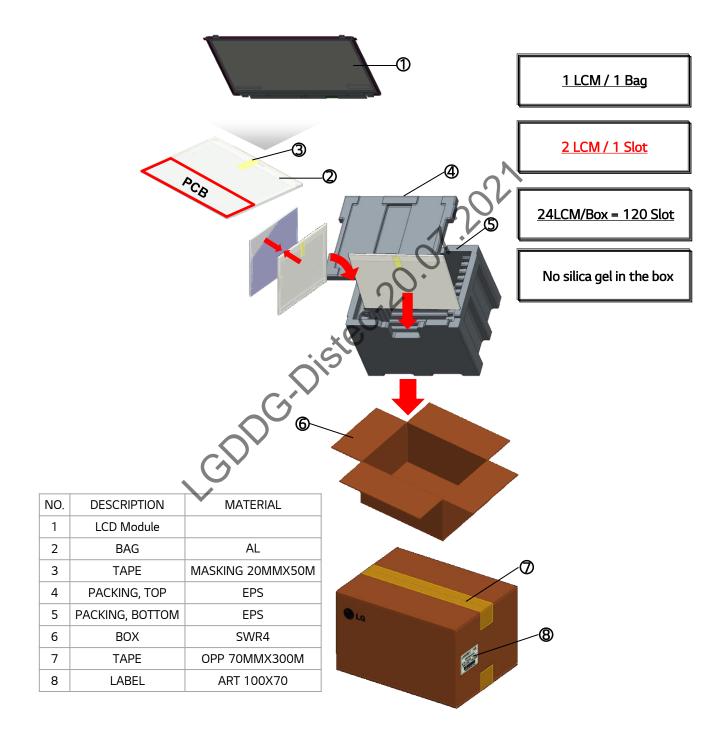

# 8-2. Packing Form

a) Package quantity in one box: 24 pcs

b) Box Size: 478 x 365 x 328

# 8-3. Packing Assembly

# 8-4. Pallet Assembly

1. Pallet Ready 2. 3 x 2 x 3 Box Pattern 3. Angle Packing & Taping 4. Banding

### 9. PRECAUTIONS

Please pay attention to the followings when you use this TFT LCD module.

### 9-1. MOUNTING PRECAUTIONS

- (1) You must mount a module using holes arranged in four corners or four sides.

- (2) You should consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to the module. And the case on which a module is mounted should have sufficient strength so that external force is not transmitted directly to the module.

- (3) Please attach the surface transparent protective plate to the surface in order to protect the polarizer. Transparent protective plate should have sufficient strength in order to the resist external force.

- (4) You should adopt radiation structure to satisfy the temperature specification.

- (5) Acetic acid type and chlorine type materials for the cover case are not desirable because the former generates corrosive gas of attacking the polarizer at high temperature and the latter causes circuit break by electro-chemical reaction.

- (6) Do not touch, push or rub the exposed polarizers with glass, tweezers or anything harder than HB pencil lead. And please do not rub with dust clothes with chemical treatment.

- Do not touch the surface of polarizer for bare hand or greasy cloth.(Some cosmetics are detrimental to the polarizer.)

- (7) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like chamois soaks with petroleum benzene. Normal hexane is recommended for cleaning the adhesives used to attach front / rear polarizers. Do not use acetone, toluene and alcohol because they cause chemical damage to the polarizer.

- (8) Wipe off saliva or water drops as soon as possible. Their long time contact with polarizer causes deformations and color fading.

- (9) Do not open the case because inside circuits do not have sufficient strength.

- (10) When handling the LCD module, it needs to handle with care not to give mechanical stress to the PCB and Mounting Hole area."

# 9-2. OPERATING PRECAUTIONS

- (1) The spike noise causes the mis-operation of circuits. It should be lower than following voltage :  $V=\pm 200 mV$ (Over and under shoot voltage)

- (2) Response time depends on the temperature.(In lower temperature, it becomes longer.)

- (3) Brightness depends on the temperature. (In lower temperature, it becomes lower.)

And in lower temperature, response time(required time that brightness is stable after turned on) becomes longer.

- (4) Be careful for condensation at sudden temperature change. Condensation makes damage to polarizer or electrical contacted parts. And after fading condensation, smear or spot will occur.

- (5) When fixed patterns are displayed for a long time, remnant image is likely to occur.

- (6) Module has high frequency circuits. Sufficient suppression to the electromagnetic interference shall be done by system manufacturers. Grounding and shielding methods may be important to minimized the interference.

Ver. 1.0 Jun. 10, 2019 28 / 29

### 9-3. ELECTROSTATIC DISCHARGE CONTROL

Since a module is composed of electronic circuits, it is not strong to electrostatic discharge. Make certain that treatment persons are connected to ground through wrist band etc. And don't touch interface pin directly.

### 9-4. PRECAUTIONS FOR STRONG LIGHT EXPOSURE

Strong light exposure causes degradation of polarizer and color filter.

### 9-5. STORAGE

When storing modules as spares for a long time, the following precautions are necessary.

- (1) Store them in a dark place. Do not expose the module to sunlight or fluorescent light. Keep the temperature between 5°C and 35°C at normal humidity.

- (2) The polarizer surface should not come in contact with any other object.

It is recommended that they be stored in the container in which they were shipped.

# 9-6. HANDLING PRECAUTIONS FOR PROTECTION FILM

- (1) When the protection film is peeled off, static electricity is generated between the film and polarizer. This should be peeled off slowly and carefully by people who are electrically grounded and with well ion-blown equipment or in such a condition, etc.

- (2) The protection film is attached to the polarizer with a small amount of glue. If some stress is applied to rub the protection film against the polarizer during the time you peel off the film, the glue is apt to remain on the polarizer.

- Please carefully peel off the protection film without rubbing it against the polarizer.

- (3) When the module with protection film attached is stored for a long time, sometimes there remains a very small amount of glue still on the polarizer after the protection film is peeled off.

- (4) You can remove the glue easily. When the glue remains on the polarizer surface or its vestige is recognized, please wipe them off with absorbent cotton waste or other soft material like chamois soaked with normal-hexane.

### 9-7. THE LGD QA RESPONSIBILITY WILL BE AVOIDED IN CASE OF BELOW

- (1) When the customer attaches TSM(Touch Sensor Module) on LCM without Supplier's approval.

- (2) When the customer attaches cover glass on LCM without Supplier's approval.

- (3) When the LCMs were repaired by 3rd party without Supplier's approval.

- (4) When the LCMs were treated like Disassemble and Rework by the Customer and/or Customer's representatives without supplier's approval.

Ver. 1.0 Jun. 10, 2019 29 / 29

Our company network supports you worldwide with offices in Germany, Austria, Switzerland, the UK and the USA. For more information please contact:

Headquarters

### Germany

### FORTEC Elektronik AG

Augsburger Str. 2b 82110 Germering

Phone: +49 89 894450-0

E-Mail: info@fortecag.de

Internet: www.fortecag.de

**Fortec Group Members**

### Austria

### Distec GmbH Office Vienna

Nuschinggasse 12 1230 Wien

Phone: +43 1 8673492-0

E-Mail: info@distec.de

Internet: www.distec.de

### Germany

### Distec GmbH

Augsburger Str. 2b 82110 Germering

Phone: +49 89 894363-0

E-Mail: info@distec.de

www.distec.de

# Switzerland

### ALTRAC AG

Bahnhofstraße 3 5436 Würenlos

Phone:

+41 44 7446111

E-Mail:

info@altrac.ch

Internet:

www.altrac.ch

### **United Kingdom**

### Display Technology Ltd.

Osprey House, 1 Osprey Court Hichingbrooke Business Park Huntingdon, Cambridgeshire, PE29 6FN

Phone: +44 1480 411600

E-Mail: info@displaytechnology.co.uk

Internet: www.displaytechnology.co.uk

### USA

### Apollo Display Technologies, Corp.

87 Raynor Avenue, Unit 1Ronkonkoma, NY 11779

Phone: +1 631 5804360

E-Mail: info@apollodisplays.com

Internet: www.apollodisplays.com