# Manual

# **ADVANTECH**

SOM-2532

The information contained in this document has been carefully researched and is, to the best of our knowledge, accurate. However, we assume no liability for any product failures or damages, immediate or consequential, resulting from the use of the information provided herein. Our products are not intended for use in systems in which failures of product could result in personal injury. All trademarks mentioned herein are property of their respective owners. All specifications are subject to change without notice.

# CarrierBoard Design Guide

SOM-2532

R020 2020'09'29

### Contents

| 1   | Intro                    | duction                                                           | 9 |   |  |  |

|-----|--------------------------|-------------------------------------------------------------------|---|---|--|--|

| 1.1 | Ab                       | out This Document                                                 | 9 |   |  |  |

| 1.2 | Signal Table Terminology |                                                                   |   |   |  |  |

| 1.3 | Tei                      | minology                                                          | 1 | 0 |  |  |

| 1.4 | Re                       | ference Documents                                                 | 1 | 3 |  |  |

| 1.5 | Re                       | vision History                                                    | 1 | 3 |  |  |

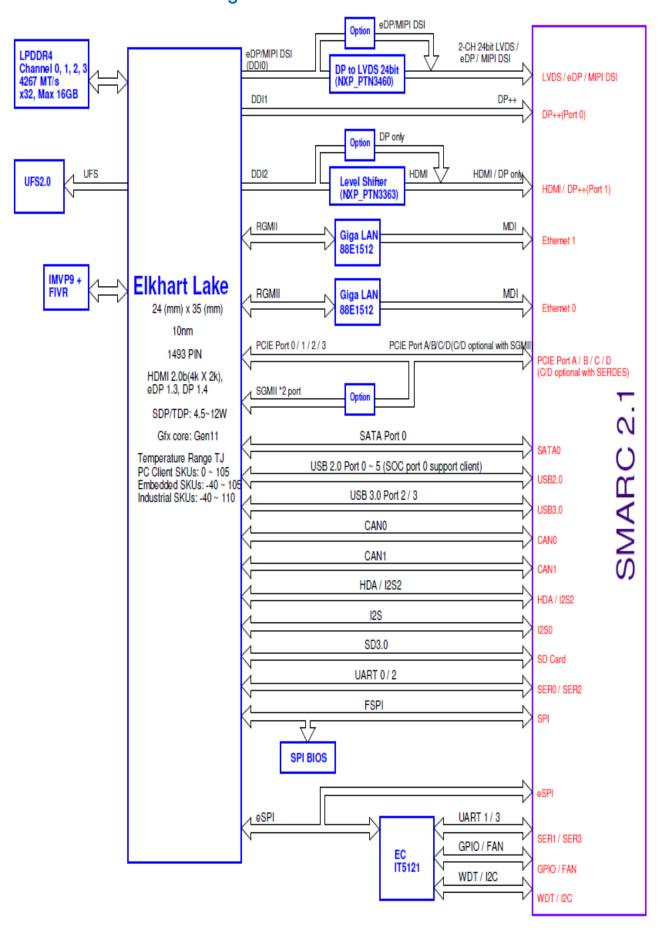

| 1.6 |                          | M-2532 Block Diagram                                              |   |   |  |  |

|     |                          | RC Interfaces                                                     |   |   |  |  |

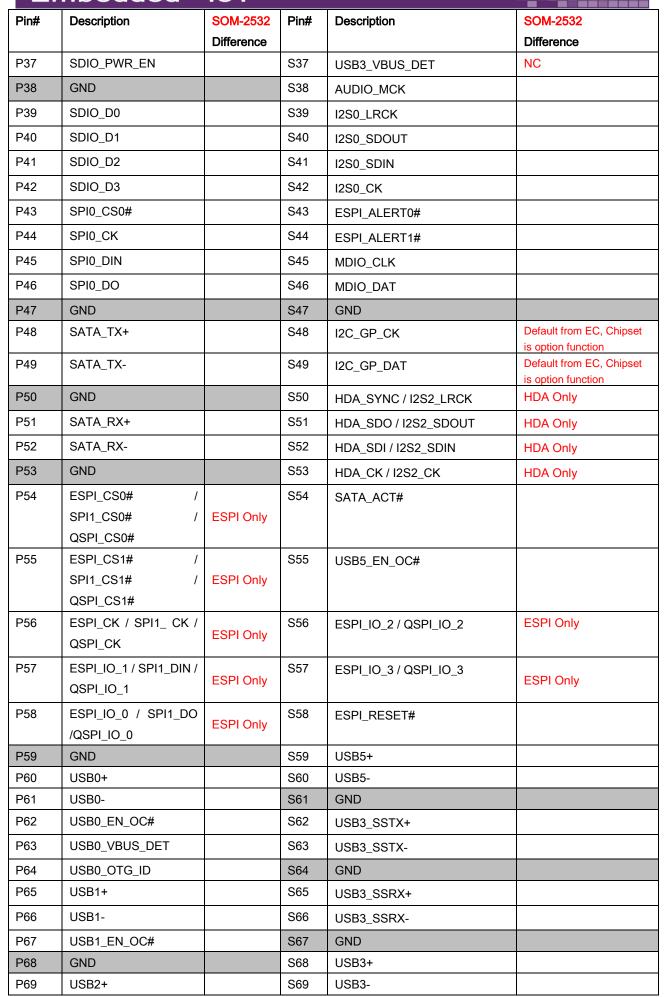

| 2.1 |                          | IARC 2.1 Connector Pin-out                                        |   |   |  |  |

|     |                          |                                                                   |   |   |  |  |

| 2.2 |                          | I Express                                                         |   |   |  |  |

|     | 2.2.1                    | PCIe Groups PCI Express Link Width                                |   |   |  |  |

|     | 2.2.2                    | ·                                                                 |   |   |  |  |

|     | _                        | PCI Express* General Routing Guidelines                           |   |   |  |  |

|     |                          | 2.2.4.1 PCI Express Differential Transitional Via Recommendations |   |   |  |  |

|     |                          | 2.2.4.2 PCIe x1 Device Down on Carrier                            |   |   |  |  |

|     |                          | 2.2.4.3 Mini-PCle Slot                                            |   |   |  |  |

|     | 2.2.5                    | PCI Express* Trace Length Guidelines                              | 2 | 9 |  |  |

| 2.3 | SE                       | RDES *SOM-2532 is Option function                                 | 3 | 2 |  |  |

|     | 2.3.1                    | SERDES Signal Definitions                                         | 3 | 2 |  |  |

|     | 2.3.2                    | SERDES General Routing Guidelines                                 | 3 | 3 |  |  |

|     | 2.3.3                    | SERDES Trace Length Guidelines                                    | 3 | 3 |  |  |

| 2.4 | LA                       | N Interface                                                       | 3 | 5 |  |  |

|     | 2.4.1                    | LAN Signal Definitions                                            | 3 | 5 |  |  |

|     | 2.4.2                    | SDP Pins                                                          | 3 | 9 |  |  |

|     | 2.4.3                    | LAN Implementation Guidelines                                     | 4 | 0 |  |  |

|     | 2.4.4                    | LAN Magnetics Modules                                             | 4 | 0 |  |  |

|     | 2.4.5                    |                                                                   |   |   |  |  |

|     | 2.4.6                    | •                                                                 |   |   |  |  |

|     | 2.4.7                    | ,                                                                 |   |   |  |  |

|     | 2.4.8                    | LAN Trace Length Guidelines                                       |   |   |  |  |

| • - | 2.4.9                    | <b>3</b>                                                          |   |   |  |  |

| 2.5 |                          | TA                                                                |   |   |  |  |

|     | 2.5.1                    | SATA Signal Definitions                                           | 4 | 5 |  |  |

|     | 2.5.2 | SATA     | Application                                                 | 4 | 5 |

|-----|-------|----------|-------------------------------------------------------------|---|---|

|     | 2.5.3 | SATA     | Routing Guidelines                                          | 4 | 6 |

|     | 2     | 2.5.3.1  | General SATA Routing Guidelines                             | 4 | 6 |

|     | 2     | 2.5.3.2  | SATA Differential Transitional Via Recommendations          | 4 | 6 |

|     | 2.5.4 | SATA     | Trace Length Guidelines                                     | 4 | 7 |

| 2.6 | USI   | 3 Interf | ace                                                         | 4 | 8 |

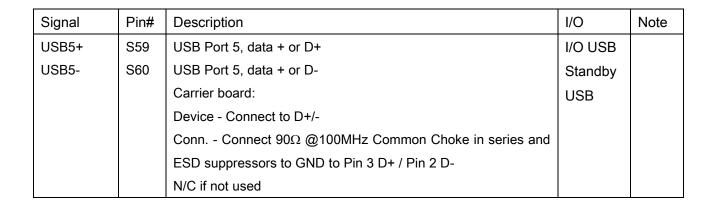

|     | 2.6.1 | USB S    | ignal Assignments                                           | 4 | 8 |

|     | 2.6.2 | USB2.    | 0 Signal Definitions                                        | 4 | 9 |

|     | 2     | 2.6.2.1  | USB[0:5]_EN_OC# Discussion                                  | 5 | 3 |

|     | 2     | 2.6.2.2  | Powering USB devices during S5                              | 5 | 3 |

|     | 2.6.3 | USB2.    | 0 Routing Guidelines                                        | 5 | 4 |

|     | 2     | 2.6.3.1  | USB 2.0 General Design Considerations and Optimization      | 5 | 4 |

|     | 2     | 2.6.3.2  | USB 2.0 Port Power Delivery                                 | 5 | 4 |

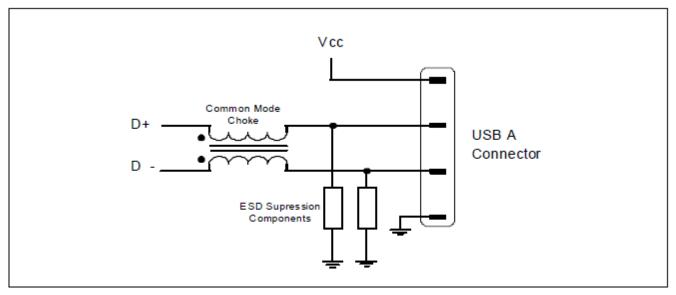

|     | 2     | 2.6.3.3  | USB 2.0 Common Mode Chokes                                  | 5 | 5 |

|     | 2     | 2.6.3.4  | EMI / ESD Protection                                        | 5 | 6 |

|     | 2     | 2.6.3.5  | USB0 Client / Host Direct From Module                       | 5 | 6 |

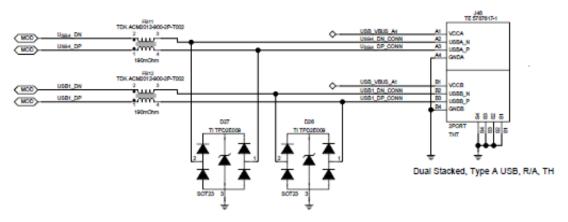

|     | 2     | 2.6.3.6  | USB1 and USB2 Host Ports direct from Module                 | 5 | 7 |

|     | 2.6.4 | USB2.    | 0 Trace Length Guidelines                                   | 5 | 8 |

|     | 2.6.5 | USB3.    | 2 General:                                                  | 5 | 9 |

|     | 2.6.6 | USB3.    | 2 Signal Definitions                                        | 5 | 9 |

|     | 2.6.7 | USB3.    | 2 Routing Guidelines                                        | 6 | 1 |

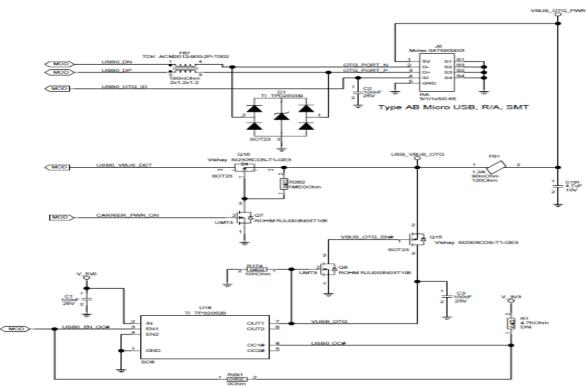

|     | 2     | 2.6.7.1  | USB3.2 OTG                                                  | 6 | 2 |

|     | 2     | 2.6.7.2  | EMI / ESD Protection                                        | 6 | 3 |

|     | 2     | 2.6.7.3  | USB3.0/USB3.2 Differential Transitional Via Recommendations | 6 | 3 |

|     |       |          | USB3.2 General Guidelines                                   |   |   |

|     | 2.6.8 | USB3.    | 2 Trace Length Guidelines                                   | 6 | 5 |

| 2.7 | SDI   | O Inter  | face                                                        | 6 | 6 |

|     | 2.7.1 | SDIO S   | Signal Definitions                                          | 6 | 6 |

|     | 2.7.2 | SDIO I   | nterface Routing Guidelines                                 | 6 | 8 |

| 2.8 | Auc   | lio HDA  | A / I2S                                                     | 6 | 9 |

|     | 2.8.1 | HDA /    | I2S Signal Descriptions                                     | 7 | 0 |

|     | 2     | 2.8.1.1  | I2S Signal Descriptions                                     | 7 | 0 |

|     | 2     | 2.8.1.2  | HDA / I2S Signal Descriptions                               | 7 | 1 |

|     | 2.8.2 | Audio    | Routing Guidelines                                          | 7 | 2 |

|     | 2.8.3 | HDA /    | I2S Trace Length Guidelines                                 | 7 | 3 |

|     | 2     | 2.8.3.1  | HDA Trace Length Guidelines                                 | 7 | 3 |

|     | 2     | 2.8.3.2  | I2S Trace Length Guidelines                                 | 7 | 4 |

| 2.9 | Ľ    | VD9  | 3      |                                                        | 7 | 5   |

|-----|------|------|--------|--------------------------------------------------------|---|-----|

|     | 2.9. | .1   | Signal | Definitions                                            | 7 | 6   |

|     |      | 2.9  | 9.1.1  | Display Timing Configuration                           | 7 | 9   |

|     |      | 2.9  | 9.1.2  | Backlight Control                                      | 7 | 9   |

|     | 2.9. | .2   | LVDS   | Routing Guidelines                                     | 7 | 9   |

|     | 2.9. | .3   | LVDS   | Trace Length Guidelines                                | 8 | 0   |

| 2.1 | 0 I  | Eml  | bedde  | ed DisplayPort (eDP) *SOM-2532 is Option function      | 8 | 1   |

|     | 2.10 | 0.1  | eDP \$ | Signal Definitions                                     | 8 | 1   |

|     |      | 2.   | 10.1.1 | LVDS / eDP Pin Sharing                                 | 8 | 5   |

|     | 2.10 | 0.2  | eDP I  | mplementation Guidelines                               | 8 | 6   |

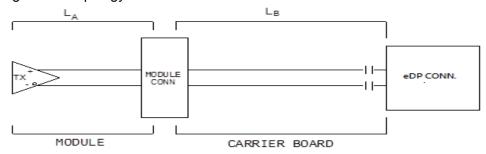

|     | 2.10 | 0.3  | eDP 7  | Trace Length Guidelines                                | 8 | 7   |

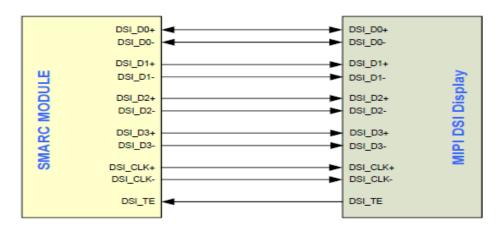

| 2.1 | 1 I  | MIP  | I DSI  | *SOM-2532 is Option function                           | 8 | 8   |

|     | 2.1  | 1.1  | DSI S  | Signal Definitions                                     | 8 | 8   |

|     |      | 2.   | 11.1.1 | LVDS / DSI Pin Sharing                                 | 9 | 1   |

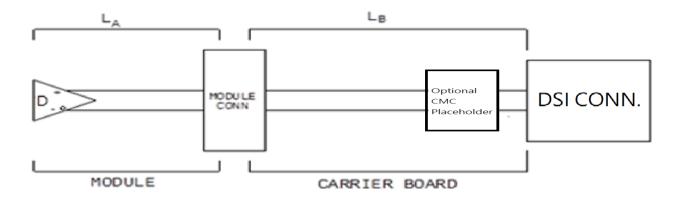

|     | 2.1  | 1.2  | DSI T  | opology Guidelines                                     | 9 | 1   |

|     | 2.1  | 1.3  | DSI T  | race Length Guidelines                                 | 9 | 2   |

| 2.1 | 2 I  | Disp | olayP  | ort(DP) / HDMI Interfaces *SOM-2532 is Option function | 9 | 3   |

|     | 2.12 | 2.1  | Displa | ayPort / HDMI Interface Signals (from Module)          | 9 | 3   |

|     | 2.12 | 2.2  | DP++   | ·                                                      | 9 | 8   |

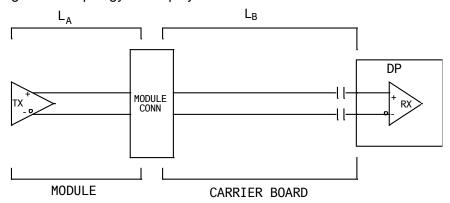

|     | 2.12 | 2.3  | Displa | ayPort Interfaces Routing Guidelines                   | 1 | 0 1 |

|     |      | 2.   | 12.3.1 | DisplayPort Routing Guidelines                         | 1 | 0 1 |

|     |      | 2.   | 12.3.2 | HDMI Routing Guidelines                                | 1 | 0 3 |

|     | 2.12 | 2.4  | ESD    | Protection                                             | 1 | 0 5 |

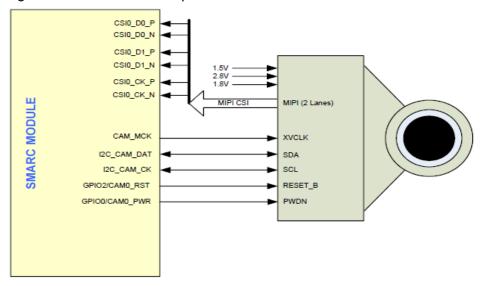

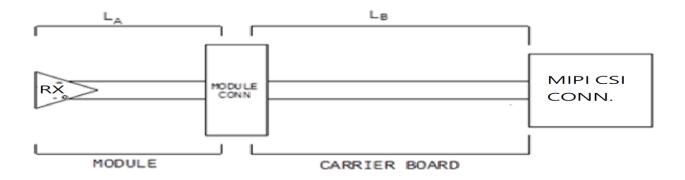

| 2.1 | 3 (  | Car  | nera I | nterfaces(MIPI CSI) SOM-2532 is no support CSI         | 1 | 0 6 |

|     | 2.13 | 3.1  | Came   | era Configurations                                     | 1 | 0 7 |

|     | 2.13 | 3.2  | Came   | era Signal Definition                                  | 1 | 0 7 |

|     | 2.13 | 3.3  | Seria  | Camera Interface Example                               | 1 | 1 1 |

|     | 2.13 | 3.4  | Other  | Camera Options                                         | 1 | 1 1 |

|     | 2.13 | 3.5  | Came   | era (MIPI CSI) Routing Guidelines                      | 1 | 1 2 |

|     | 2.13 | 3.6  | Came   | era (MIPI CSI) Trace Length Guidelines                 | 1 | 1 2 |

|     | 2.13 | 3.7  | Came   | era (MIPI CSI) – Connector and Cable                   | 1 | 1 3 |

| 2.1 | 4 (  | CAI  | ۱ Inte | rface                                                  | 1 | 1 4 |

|     | 2.14 | 4.1  | CAN    | interface Signal Definitions                           | 1 | 1 5 |

|     | 2.14 | 4.2  | CAN    | interface Routing Guidelines                           | 1 | 1 6 |

|     | 2.14 | 4.3  | CAN    | interface Trace Length Guidelines                      | 1 | 1 6 |

| 2.1 | 5 \$ | SPI  | – Sei  | rial Peripheral Interface Bus                          | 1 | 1 7 |

|     | 2.1  | 5.1  | SPI0   | Signal Definition                                      | 1 | 1 7 |

### Embedded - IoT 2.15.2 QSPI Signal Definition \*SOM-2532 is not supported QSPI...... 1 2 0 2.15.3 2.18.1 2.20 Miscellaneous Signals ...... 1 3 5 2.20.1 Miscellaneous Signals...... 1 3 5 2.20.1.1 Watchdog Control Signals...... 1 3 8 2.22.1 2.22.2 Boot Selection Signals ...... 1 4 2 2.22.3

### Embedded - IoT 2.23.1 2.23.2 3.1 Input Voltage / Main Power Rail...... 1 4 6 3.2 No Separate Standby Voltage ...... 1 4 6 3.3 RTC Voltage Rail ...... 1 4 6 Power Sequencing...... 1 4 8 System Power Domains...... 1 5 0 4.1. Absolute Maximum Ratings...... 1 5 1

### **List of Tables**

| Table 1: Signal Direction and Type Definitions                              | · • • • | 9 |

|-----------------------------------------------------------------------------|---------|---|

| Table 2: Conventions and Terminology                                        | 1       | 0 |

| Table 3: SMARC 2.1 Pin-out                                                  | 1       | 5 |

| Table 4: PCIe Data Transfer Rates                                           | 2       | 1 |

| Table 5: PCI Express Link Width                                             | 2       | 2 |

| Table 6: General Purpose PCI Express Signal Descriptions                    | 2       | 3 |

| Table 7: Differential Transitional Via Layout Recommendations               | 2       | 7 |

| Table 8: PCI Express Gen2* Slot Card / Device Down Trace Length Guidelines  | 3       | 0 |

| Table 9: PCI Express Gen3 * Slot Card / Device Down Trace Length Guidelines | 3       | 1 |

| Table 10: SERDES Interface Signal Descriptions                              | 3       | 2 |

| Table 11: SERDES Trace Length Guidelines                                    | 3       | 4 |

| Table 12: LAN Interface Signal Descriptions                                 | 3       | 5 |

| Table 13: The MDI can operate in 1000, 100 and 10 Mbit / sec modes          | 3       | 8 |

| Table 14: Ethernet Trace Length Guidelines                                  | 4       | 3 |

| Table 15: SATA Signal Definitions                                           | 4       | 5 |

| Table 16: SATA Trace Length Guidelines                                      | 4       | 7 |

| Table 17: USB Signal Assignments                                            | 4       | 8 |

| Table 18: USB2.0 Signal Descriptions                                        | 4       | 9 |

| Table 19: USB2.0 Trace Length Guidelines                                    | 5       | 8 |

| Table 20: USB3.0 Signal Definitions                                         | 5       | 9 |

| Table 21: USB3.2 Trace Length Guidelines                                    | 6       | 5 |

| Table 22: Signal Definition SDIO                                            | 6       | 6 |

| Table 23: SDIO Trace Length Guidelines                                      | 6       | 8 |

| Table 24: I2S Signal Descriptions                                           | 7       | 0 |

| Table 25: HDA/I2S Signal Descriptions                                       | 7       | 1 |

| Table 26: HDA Trace Length Guidelines                                       | 7       | 3 |

| Table 27: I2S Trace Length Guidelines                                       | 7       | 4 |

| Table 28: LVDS Signal Definitions                                           | 7       | 6 |

| Table 29: LVDS Trace Length Guidelines                                      | 8       | 0 |

| Table 30: eDP Signal Definitions                                            | 8       | 1 |

| Table 31: LVDS / eDP Pin Sharing                                            | 8       | 5 |

| Table 32: DisplayPort Connector / Device Down Trace Length Guidelines       | 8       | 7 |

| Table 33: DSI Signal Definitions                                            | 8       | 8 |

| Table 34: LVDS / DSI Pin Sharing                                        | 9   | 1   |

|-------------------------------------------------------------------------|-----|-----|

| Table 35: DSI Connector / Device Down Trace Length Guidelines           | g   | 2   |

| Table 36: Signal Definition DisplayPort / HDMI                          | 9   | 4   |

| Table 37: Signal Definition DP++                                        | 9   | 8 ( |

| Table 38: DisplayPort Connector / Device Down Trace Length Guidelines 1 | 1 C | 2   |

| Table 39: HDMI Connector / Device Down Trace Length Guidelines 1        | 1 C | ) 4 |

| Table 40: Camera Interface Signal Definition1                           | 1 C | 7   |

| Table 41: MIPI CSI Trace Length Guidelines                              | 1 1 | 1 2 |

| Table 42: MIPI CSI Connector and Cable Requirement                      | 1 1 | 1 3 |

| Table 43: CAN interface Signal Definitions1                             | 1 1 | 1 5 |

| Table 44: CAN interface Trace Length Guidelines1                        | 1 1 | 1 6 |

| Table 45: SPIO Interface Signal Definition                              | 1 1 | 1 7 |

| Table 46: SPI1 Interface Signal Definition                              | 1 1 | 1 9 |

| Table 47: QSPI Interface Signal Definition1                             | 1 2 | 2 0 |

| Table 48: SPI Trace Length Guidelines 1                                 | 1 2 | 2 1 |

| Table 49: eSPI Interface Signal Definition1                             | 1 2 | 2 2 |

| Table 50: eSPI Trace Length Guidelines                                  | 1 2 | 2 5 |

| Table 51: Six I2C interfaces 1                                          | 1 2 | 2 6 |

| Table 52: General Purpose I2C Interface Signal Descriptions 1           | 1 2 | 2 7 |

| Table 53: PM I2C Interface Signal Descriptions1                         | 1 2 | 2 8 |

| Table 54: I2C Trace Length Guidelines 1                                 | 1 2 | 2 9 |

| Table 55: Serial interface Signal Definitions                           | 1 3 | 3 1 |

| Table 56: Serial interface Trace Length Guidelines1                     | 1 3 | 3   |

| Table 57: GPIO Signals, Pin Types, and Descriptions1                    | 1 3 | 3 4 |

| Table 58: Miscellaneous Signal Definitions1                             | 1 3 | 3 5 |

| Table 59: Fan Control Signal Definitions                                | 1 3 | 3 9 |

| Table 60: Boot Selection Signals Descriptions1                          | 1 4 | 1 2 |

| Table 61: Boot Select Pins                                              | 1 4 | 1 3 |

| Table 62: Power and GND1                                                | 1 4 | 1 5 |

| Table 63: Power Management Timings1                                     | 1 4 | 1 8 |

| Table 64: Absolute Maximum Ratings 1                                    | 1 5 | 5 1 |

| Table 65: Input Power Consumption of 5V 1                               | 1 5 | 5 1 |

| Table 66: Inrush Current                                                | 1 5 | . 1 |

# List of Figures

| Figure 1: Differential Transitional Via Layout         | 2 | 7 |

|--------------------------------------------------------|---|---|

| Figure 2: Interfacing a PCIe x1 Carrier Board Device   | 2 | 8 |

| Figure 3: Mini-PCle Slot                               | 2 | 8 |

| Figure 4: Topology for PCI Express Slot Card           | 2 | 9 |

| Figure 5: Topology for PCI Express Device Down         | 2 | 9 |

| Figure 6: Topology for SERDES Device Down              | 3 | 3 |

| Figure 7: LAN Ground Plane Separation                  | 4 | 1 |

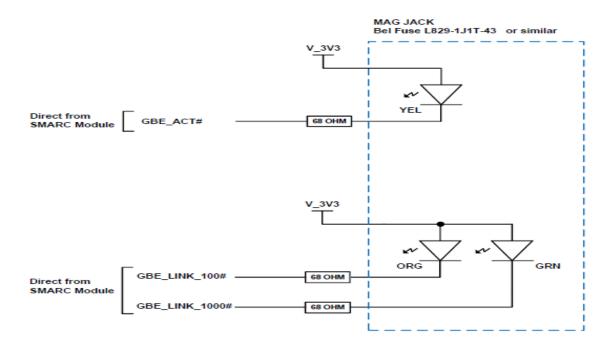

| Figure 8: GBE LED Current Sink                         | 4 | 2 |

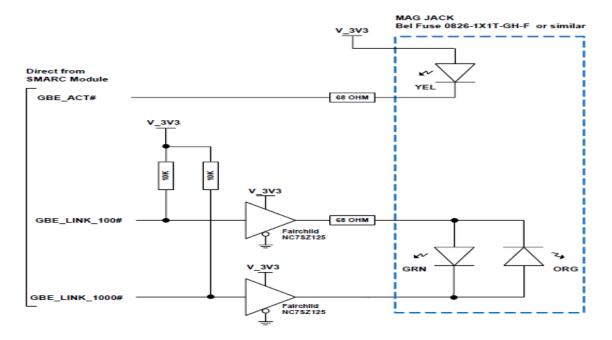

| Figure 9: GBE LED Current Sink / Source                | 4 | 2 |

| Figure 10: Topology for Ethernet Jack                  | 4 | 3 |

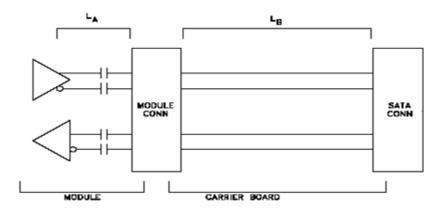

| Figure 11: Topology for SATA                           | 4 | 7 |

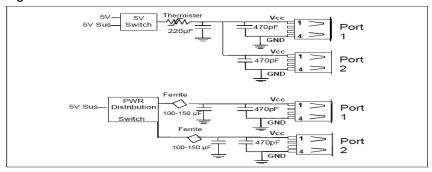

| Figure 12: USB 2.0 Good Downstream Power Connection    | 5 | 4 |

| Figure 13: USB 2.0 A Common Mode Choke                 | 5 | 5 |

| Figure 14: USB0 Client / Host Direct From Module       | 5 | 6 |

| Figure 15: USB1 and USB4 Host Ports Direct From Module | 5 | 7 |

| Figure 16: Topology for USB2.0                         | 5 | 8 |

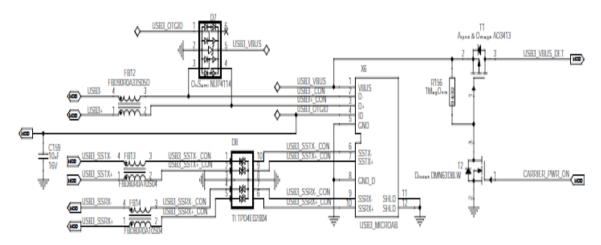

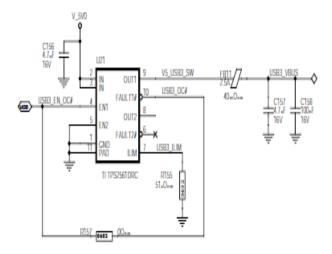

| Figure 17: USB 3.2 host dual                           | 6 | 1 |

| Figure 18: USB3.2 OTG                                  | 6 | 2 |

| Figure 19: Topology for USB3.2                         | 6 | 5 |

| Figure 20: Topology for SDIO                           | 6 | 8 |

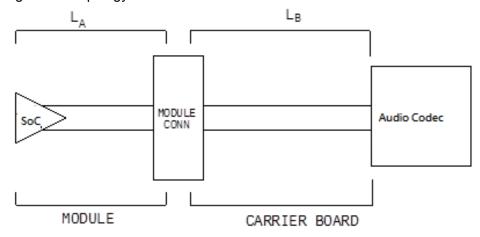

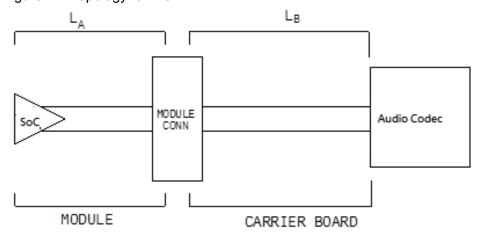

| Figure 21: Topology for HDA                            | 7 | 3 |

| Figure 22: Topology for I2S                            | 7 | 4 |

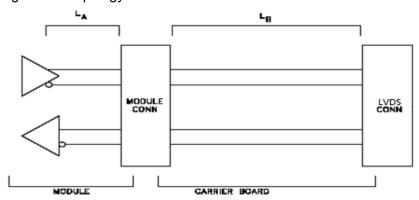

| Figure 23: Topology for LVDS                           | 8 | 0 |

| Figure 24: Topology for eDP                            | 8 | 7 |

| Figure 25: MIPI DSI                                    | 8 | 8 |

| Figure 26: Topology for DSI                            | 9 | 2 |

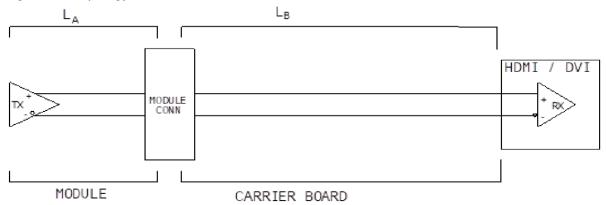

| Figure 27: Topology for DisplayPort                    | 0 | 2 |

| Figure 28: Topology for HDMI                           | 0 | 4 |

| Figure 29: Serial Camera Implementation                | 1 | 1 |

| Figure 30: Topology for MIPI CSI                       | 1 | 2 |

| Figure 31: Topology for CAN interface                  | 1 | 6 |

| Figure 32: Topology for SPI                            | 2 | 1 |

| Figure 33: Topology for eSPI                           | 2 | 5 |

| Figure 34: Topology for I2C              | 1 | 2 | 9 |

|------------------------------------------|---|---|---|

| Figure 35: Topology for Serial interface | 1 | 3 | 3 |

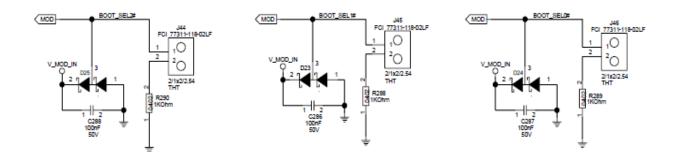

| Figure 36: Boot Selection Jumpers        | 1 | 4 | 3 |

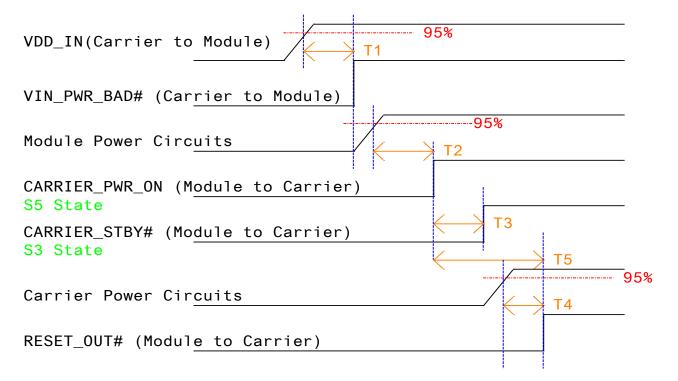

| Figure 37: Power On Sequencing           | 1 | 4 | 8 |

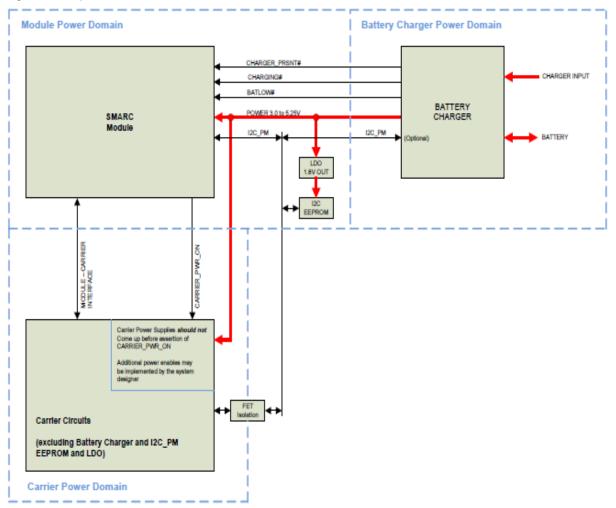

| Figure 38: System Power Domains          | 1 | 5 | 0 |

### 1 Introduction

#### 1.1 About This Document

This document provides information for designing a custom system carrier board for SMARC modules. It includes Signal Descriptions, Routing Guidelines and Trace Length Guidelines. The main purpose is designing Carrier Board for helping customers fast and easy using the module of Advantech to be designed.

### 1.2 Signal Table Terminology

Table 1 below describes the terminology used in this section for the Signal Description tables.

The terms "Input" and "Output" and their abbreviations in Table 1 below refer to the Module's view, i.e. an input is an input for the Module and not for the Carrier-Board.

Table 1: Signal Direction and Type Definitions

| Term        | Description                                                                    |

|-------------|--------------------------------------------------------------------------------|

| I           | Input to the Module                                                            |

| 0           | Output from the Module                                                         |

| I/O         | Bi-directional input/output                                                    |

| OD          | Open drain                                                                     |

| PU          | PU (pull-up) resistor                                                          |

| PD          | PD (pull-down) resistor                                                        |

| CMOS        | Logic input or output                                                          |

| GBE MDI     | Differential analog signaling for gigabit media dependent interface            |

| DP          | Low voltage differential signal for DisplayPort interface                      |

| D-PHY       | Low voltage differential signal for MIPI CSI-2 cameras and DSI displays        |

| M-PHY       | Low voltage differential signal for MIPI CSI-3 cameras                         |

| LVDS        | Low voltage differential signal for LCD displays                               |

| PCIE        | Low voltage differential signal for PCIe                                       |

| SATA        | Low voltage differential signal for SATA                                       |

| TMDS HDMI   | Transition minimized differential signal for HDMI displays                     |

| USB         | DC coupled differential signaling for traditional (non-Superspeed) USB signals |

| USB SS      | Differential signal for SuperSpeed USB signals                                 |

| USB VBUS 5V | 5V tolerant input for USB VBUS detection                                       |

| VDD_IN      | Main power source from Carrier to Module                                       |

| 3.3V        | 3.3V power domain: Active while CARRIER_PWRON is high and CARRIER_SBY# is      |

|             | NOT active (i.e. both signals are high)                                        |

| 1.8V        | 1.8V power domain: Active while CARRIER_PWRON is high and CARRIER_SBY# is      |

|             | NOT active (i.e. both signals are high)                                        |

| Embed                                                                   | Embedded - IoT                                                                |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| 3.3Vsb                                                                  | 3.3V standby power domain: Active while CARRIER_PWRON is high (regardless of  |  |  |  |

|                                                                         | CARRIER_SBY#)                                                                 |  |  |  |

| 1.8Vsb 1.8V standby power domain: Active while CARRIER_PWRON is high (i |                                                                               |  |  |  |

|                                                                         | CARRIER_SBY#)                                                                 |  |  |  |

| Sleep                                                                   | Module is in its lowest power state                                           |  |  |  |

| Runtime                                                                 | Module is full on. CARRIER_PWRON is high and CARRIER_SBY# is NOT active (i.e. |  |  |  |

|                                                                         | both signals are high)                                                        |  |  |  |

| Standby                                                                 | Module is in Standby State or higher                                          |  |  |  |

# 1.3 Terminology

Table 2: Conventions and Terminology

| Terminology | Description                                         |

|-------------|-----------------------------------------------------|

| ADC         | Analog to Digital Converter                         |

| ARM         | Advanced RISC Machines                              |

| ВСТ         | Boot Configuration Table                            |

| BSP         | (software) Board Support Package                    |

| CAD         | Computer Aided Design                               |

| CAN         | Controller Area Network                             |

| CPLD        | Complex Programmable Logic Device                   |

| CODEC       | Coder – Decoder                                     |

| CSI         | Camera Serial Interface                             |

| DAC         | Digital to Analog Converter                         |

| DB-9        | Connector, D shaped, B shell size, 9 pins           |

| DDC         | Display Data Channel                                |

| DDI         | Digital Display Interface                           |

| DE          | Differential Ended (signal pair)                    |

| DNI         | Do Not Install (component is not loaded)            |

| DP          | DisplayPort                                         |

| DP++        | Dual-mode DisplayPort                               |

| DSP         | Digital Signal Processor                            |

| DSI         | Display Serial Interface                            |

| EDID        | Extended Display Identification Data                |

| EEPROM      | Electrically Erasable Programmable Read Only Memory |

| eMMC        | Embedded Multi Media Card                           |

| ESD         | Electro Static Discharge                            |

| FET         | Field Effect Transistor                             |

| FIFO        | First In First Out (buffer memory)                  |

| Embedded | l - IoT                                                 |

|----------|---------------------------------------------------------|

| FS       | Full Speed (USB 2.0 12 Mbps)                            |

| GBE      | Gigabit Ethernet                                        |

| Gbps     | Gigabit per second                                      |

| GPIO     | General Purpose Input / Output                          |

| GPS      | Global Positioning System                               |

| HAD      | High Definition Audio – Intel defined format            |

| HDMI     | High Definition Multimedia Interface                    |

| HID      | Human Interface Device: USB device class                |

| HS       | High Speed (USB 2.0 480 Mbps)                           |

| IC       | Integrated Circuit                                      |

| I2C      | Inter-Integrated Circuit                                |

| I2S      | Inter-Integrated Circuit – Sound                        |

| IEEE     | Institute of Electrical and Electronics Engineers       |

| Ю        | Input Output                                            |

| ISO      | International Organization for Standardization (French) |

| JEDEC    | Joint Electron Device Engineering Council               |

| JPEG     | Joint Photographic Experts Group                        |

| LED      | Light Emitting Diode                                    |

| Li-lon   | Lithium Ion (rechargeable battery technology)           |

| LVDS     | Low Voltage Differential Signaling                      |

| M2.5     | Metric 2.5mm                                            |

| M3       | Metric 3.0mm                                            |

| MAC      | Media Access Controller (e.g. logic circuits in GBE)    |

| Mbps     | Megabit per second                                      |

| MIPI     | Mobile Industry Processor Interface                     |

| MLC      | Multi Level Cell (flash memory reference)               |

| MOD      | Module (the SMARC Module) (schematic notation)          |

| MO-297   | Module Outline 297 ("Slim SATA" format)                 |

| MO-300   | Module Outline 300 (mini-PCIe Express card format)      |

| MPEG     | Motion Picture Experts Group                            |

| MXM      | Mobile pci eXpress Module                               |

| MXM3     | MXM Revision 3                                          |

| NAND     | A high density flash memory technology                  |

| ns       | Nano second (10 E -9)                                   |

| NC       | Not Connected                                           |

| OS       | Operating System                                        |

| OTG      | On the Go (USB term – device can be host or client)     |

| PCB      | Printed Circuit Board                                   |

| PHY      | Physical (transceiver) – drives cable                   |

| Embedded | - IoT                                              |

|----------|----------------------------------------------------|

| PICMG    | PCI Industrial Computer Manufacturing Group        |

| PCI      | Peripheral Component Interface                     |

| PCle     | PCI Express                                        |

| PCI-SIG  | PCI Special Interest Group                         |

| PCM      | Pulse-Code Modulation                              |

| PLL      | Phase Locked Loop                                  |

| POE      | Power Over Ethernet                                |

| ps       | Pico second (10 E -12)                             |

| PWM      | Pulse Width Modulation                             |

| RGB      | Video data in Red Green Blue pixel format          |

| ROM      | Read Only Memory                                   |

| RS232    | Recommend Standard 232 (asynchronous serial ports) |

| RS485    | Asynchronous serial data, differential, multidrop  |

| RTC      | Real Time Clock (battery backed clock and memory)  |

| SAR      | Successive Approximation Register                  |

| SATA     | Serial ATA (serial mass storage interface)         |

| SD       | Secure Digital (memory card)                       |

| SE       | Single Ended (signal, as opposed to differential)  |

| SGeT     | Standardization Group for Embedded Technologies    |

| SLC      | Single Level Cell (flash memory reference)         |

| SMARC    | Smart Mobility Architecture                        |

| SMSC     | A semiconductor company, now MICROCHIP             |

| SOC      | System On Chip                                     |

| S/PDIF   | Sony/Philips Digital Interconnect Format           |

| SPI      | Serial Peripheral Interface                        |

| SSD      | Solid State Disk                                   |

| TIM      | Thermal Interface Material                         |

| UART     | Universal Asynchronous Receiver Transmitter        |

| UL       | Underwriters Laboratories                          |

| USB      | Universal Serial Bus                               |

| VESA     | Video Electronics Standards Association            |

| WEC7     | Windows Embedded Compact 7 (an OS)                 |

| YUV      | Video data format, more common in television       |

| X5R      | Ceramic capacitor dielectric – good quality        |

| X7R      | Ceramic capacitor dielectric – best quality        |

| X86      | Intel architecture (80x86) CPUs                    |

### 1.4 Reference Documents

| Document                                       |  |  |  |  |

|------------------------------------------------|--|--|--|--|

| SMACR Design Guide 2.0 March 23, 2017          |  |  |  |  |

| SMACR Hardware Specification 2.11 May 20, 2020 |  |  |  |  |

| Intel EDS Document                             |  |  |  |  |

| Intel Layout Guide Document                    |  |  |  |  |

| ATX12V Power Supply Design Guide Rev. 2.01     |  |  |  |  |

# 1.5 Revision History

| Revision | Date        | PCB Rev. | Changes                         |

|----------|-------------|----------|---------------------------------|

| 0.10     | 09 06, 2020 | A101-1   | SOM-2532 design for SMARC R2.1  |

| 0.20     | 09 29, 2020 | A101-1   | SOM-2532 design for SMARC R2.11 |

|          |             |          |                                 |

|          |             |          |                                 |

|          |             |          |                                 |

|          |             |          |                                 |

|          |             |          |                                 |

### 1.6 SOM-2532 Block Diagram

### 2 SMARC Interfaces

### 2.1 SMARC 2.11 Connector Pin-out

Table 3: SMARC 2.11 Pin-out

#### Connector

| Pin# | Description    | SOM-2532   | Pin# | Description               | SOM-2532                  |

|------|----------------|------------|------|---------------------------|---------------------------|

|      |                | Difference |      |                           | Difference                |

| P1   | SMB_ALERT      |            | S1   | CSI1_TX+ / I2C_CAM1_CK    | NC                        |

| P2   | GND            |            | S2   | CSI1_TX- / I2C_CAM1_DAT   | NC                        |

| P3   | CSI1_CK+       | NC         | S3   | GND                       |                           |

| P4   | CSI1_CK-       | NC         | S4   | RSVD                      |                           |

| P5   | GBE1_SDP       | NC         | S5   | CSI0_TX+ / I2C_CAM0_CK    | NC                        |

| P6   | GBE0_SDP       | NC         | S6   | CAM_MCK                   | NC                        |

| P7   | CSI1_RX0+      | NC         | S7   | CSI0_TX- / I2C_CAM0_DAT   | NC                        |

| P8   | CSI1_RX0-      | NC         | S8   | CSI0_CK+                  | NC                        |

| P9   | GND            |            | S9   | CSI0_CK-                  | NC                        |

| P10  | CSI1_RX1+      | NC         | S10  | GND                       |                           |

| P11  | CSI1_RX1-      | NC         | S11  | CSI0_RX0+                 | NC                        |

| P12  | GND            |            | S12  | CSI0_RX0-                 | NC                        |

| P13  | CSI1_RX2+      | NC         | S13  | GND                       |                           |

| P14  | CSI1_RX2-      | NC         | S14  | CSI0_RX1+                 | NC                        |

| P15  | GND            |            | S15  | CSI0_RX1-                 | NC                        |

| P16  | CSI1_RX3+      | NC         | S16  | GND                       |                           |

| P17  | CSI1_RX3-      | NC         | S17  | GBE1_MDI0+                |                           |

| P18  | GND            |            | S18  | GBE1_MDI0-                |                           |

| P19  | GBE0_MDI3-     |            | S19  | GBE1_LINK100#             |                           |

| P20  | GBE0_MDI3+     |            | S20  | GBE1_MDI1+                |                           |

| P21  | GBE0_LINK100#  |            | S21  | GBE1_MDI1-                |                           |

| P22  | GBE0_LINK1000# |            | S22  | GBE1_LINK1000#            |                           |

| P23  | GBE0_MDI2-     |            | S23  | GBE1_MDI2+                |                           |

| P24  | GBE0_MDI2+     |            | S24  | GBE1_MDI2-                |                           |

| P25  | GBE0_LINK_ACT# |            | S25  | GND                       |                           |

| P26  | GBE0_MDI1-     |            | S26  | GBE1_MDI3+                |                           |

| P27  | GBE0_MDI1+     |            | S27  | GBE1_MDI3-                |                           |

| P28  | GBE0_CTREF     | NC         | S28  | GBE1_CTREF                | NC                        |

| P29  | GBE0_MDI0-     |            | S29  | PCIE_D_TX+ / SERDES_0_TX+ | SEDRES is option function |

| P30  | GBE0_MDI0+     |            | S30  | PCIE_D_TX- / SERDES_0_TX- | SEDRES is option function |

| P31  | SPI0_CS1#      |            | S31  | GBE1_LINK_ACT#            |                           |

| P32  | GND            |            | S32  | PCIE_D_RX+ / SERDES_0_RX+ | SEDRES is option function |

| P33  | SDIO_WP        |            | S33  | PCIE_D_RX- / SERDES_0_RX- | SEDRES is option function |

| P34  | SDIO_CMD       |            | S34  | GND                       |                           |

| P35  | SDIO_CD#       |            | S35  | USB4+                     |                           |

| P36  | SDIO_CK        |            | S36  | USB4-                     |                           |

| Pin# | Description   | SOM-2532<br>Difference | Pin# | Description               | SOM-2532<br>Difference    |

|------|---------------|------------------------|------|---------------------------|---------------------------|

| P70  | USB2-         |                        | S70  | GND                       |                           |

| P71  | USB2_EN_OC#   |                        | S71  | USB2_SSTX+                |                           |

| P72  | RSVD          |                        | S72  | USB2_SSTX-                |                           |

| P73  | RSVD          |                        | S73  | GND                       |                           |

| P74  | USB3_EN_OC#   |                        | S74  | USB2_SSRX+                |                           |

| P75  | PCIE_A_RST#   |                        | S75  | USB2_SSRX-                |                           |

| P76  | USB4_EN_OC#   |                        | S76  | PCIE_B_RST#               |                           |

| P77  | PCIE_B_CKREQ# |                        | S77  | PCIE_C_RST#               |                           |

| P78  | PCIE_A_CKREQ# |                        | S78  | PCIE_C_RX+ / SERDES_1_RX+ | SEDRES is option function |

| P79  | GND           |                        | S79  | PCIE_C_RX- / SERDES_1_RX- | SEDRES is option function |

| P80  | PCIE_C_REFCK+ |                        | S80  | GND                       |                           |

| P81  | PCIE_C_REFCK- |                        | S81  | PCIE_C_TX+ / SERDES_1_TX+ | SEDRES is option function |

| P82  | GND           |                        | S82  | PCIE_C_TX- / SERDES_1_TX- | SEDRES is option function |

| P83  | PCIE_A_REFCK+ |                        | S83  | GND                       |                           |

| P84  | PCIE_A_REFCK- |                        | S84  | PCIE_B_REFCK+             |                           |

| P85  | GND           |                        | S85  | PCIE_B_REFCK-             |                           |

| P86  | PCIE_A_RX+    |                        | S86  | GND                       |                           |

| P87  | PCIE_A_RX-    |                        | S87  | PCIE_B_RX+                |                           |

| P88  | GND           |                        | S88  | PCIE_B_RX-                |                           |

| P89  | PCIE_A_TX+    |                        | S89  | GND                       |                           |

| P90  | PCIE_A_TX-    |                        | S90  | PCIE_B_TX+                |                           |

| P91  | GND           |                        | S91  | PCIE_B_TX-                |                           |

| P92  | HDMI_D2+ /    | DP is option           | S92  | GND                       |                           |

|      | DP1_LANE0+    | function               |      |                           |                           |

| P93  | HDMI_D2- /    | DP is option           | S93  | DP0_LANE0+                |                           |

|      | DP1_LANE0-    | function               |      |                           |                           |

| P94  | GND           |                        | S94  | DP0_LANE0-                |                           |

| P95  | HDMI_D1+ /    | DP is option           | S95  | DP0_AUX_SEL               |                           |

|      | DP1_LANE1+    | function               |      |                           |                           |

| P96  | HDMI_D1- /    | DP is option           | S96  | DP0_LANE1+                |                           |

|      | DP1_LANE1-    | function               |      |                           |                           |

| P97  | GND           |                        | S97  | DP0_LANE1-                |                           |

| P98  | HDMI_D0+ /    | DP is option           | S98  | DP0_HPD                   |                           |

|      | DP1_LANE2+    | function               |      |                           |                           |

| P99  | HDMI_D0- /    | DP is option           | S99  | DP0_LANE2+                |                           |

|      | DP1_LANE2-    | function               |      |                           |                           |

| P100 | GND           |                        | S100 | DP0_LANE2-                |                           |

| Pin# | Description       | SOM-2532            | Pin# | Description             | SOM-2532                   |

|------|-------------------|---------------------|------|-------------------------|----------------------------|

|      |                   | Difference          |      | ·                       | Difference                 |

| P101 | HDMI_CK+ /        | DP is option        | S101 | GND                     |                            |

|      | DP1_LANE3+        | function            |      |                         |                            |

| P102 | HDMI_CK-/         | DP is option        | S102 | DP0_LANE3+              |                            |

|      | DP1_LANE3-        | function            |      |                         |                            |

| P103 | GND               |                     | S103 | DP0_LANE3-              |                            |

| P104 | HDMI_HPD /        | DP is option        | S104 | USB3_OTG_ID             | NC                         |

|      | DP1_HPD           | function            |      |                         |                            |

| P105 | HDMI_CTRL_CK /    | DP is option        | S105 | DP0_AUX+                |                            |

|      | DP1_AUX+          | function            |      | _                       |                            |

| P106 | HDMI_CTRL_DAT /   | DP is option        | S106 | DP0_AUX-                |                            |

|      | DP1_AUX-          | function            |      | 1_ 1                    |                            |

| P107 | DP1_AUX_SEL       |                     | S107 | LCD1_BKLT_EN            |                            |

| P108 | GPIO0 / CAM0_PWR# | GPIO Only           | S108 | LVDS1_CK+ / eDP1_AUX+ / | LVDS Only                  |

|      |                   | Or 10 Omy           |      | DSI1_CLK+               | If eDP0 or DSI0            |

|      |                   |                     |      | DOIT_CERT               | function is used, this pin |

|      |                   |                     |      |                         | will be no function.       |

| P109 | GPIO1 / CAM1_PWR# | GPIO Only           | S109 | LVDS1_CK- / eDP1_AUX- / | LVDS Only                  |

|      |                   |                     |      | DSI1_CLK-               | If eDP0 or DSI0            |

|      |                   |                     |      | _                       | function is used, this pin |

|      |                   |                     |      |                         | will be no function.       |

| P110 | GPIO2 / CAM0_RST# | GPIO Only           | S110 | GND                     |                            |

| P111 | GPIO3 / CAM1_RST# | GPIO Only           | S111 | LVDS1_0+ / eDP1_TX0+ /  | LVDS Only                  |

|      |                   |                     |      | DSI1_D0+                | If eDP0 or DSI0            |

|      |                   |                     |      |                         | function is used, this pin |

|      |                   |                     |      |                         | will be no function.       |

| P112 | GPIO4 / HDA_RST#  | HDA_RST#            | S112 | LVDS1_0- / eDP1_TX0- /  | LVDS Only                  |

|      |                   |                     |      | DSI1_D0-                | If eDP0 or DSI0            |

|      |                   |                     |      |                         | function is used, this pin |

| P113 | ODIOS / DWM OUT   | Default             | S113 | -DD4 LIDD / DOM TE      | will be no function.       |

| P113 | GPIO5 / PWM_OUT   | PWM_OUT,            | 5113 | eDP1_HPD / DSI1_TE      | NC                         |

|      |                   | GPIO5 is            |      |                         |                            |

|      |                   | option function.    |      |                         |                            |

| P114 | GPIO6 / TACHIN    | Default             | S114 | LVDS1_1+ / eDP1_TX1+ /  | LVDS Only                  |

|      |                   | TACHIN,<br>GPIO6 is |      | DSI1_D1+                | If eDP0 or DSI0            |

|      |                   | option function     |      |                         | function is used, this pin |

|      |                   |                     |      |                         | will be no function.       |

| P115 | GPIO7             |                     | S115 | LVDS1_1- / eDP1_TX1- /  | LVDS Only                  |

|      |                   |                     |      | DSI1_D1-                | If eDP0 or DSI0            |

|      |                   |                     |      |                         | function is used, this pin |

|      |                   |                     |      |                         | will be no function.       |

| Pin#   | Description | SOM-2532   | Pin#  | Description             | SOM-2532                                      |

|--------|-------------|------------|-------|-------------------------|-----------------------------------------------|

|        |             | Difference |       |                         | Difference                                    |

| P116   | GPIO8       |            | S116  | LCD1_VDD_EN             |                                               |

| P117   | GPIO9       |            | S117  | LVDS1_2+ / eDP1_TX2+ /  | LVDS Only                                     |

|        |             |            |       | DSI1_D2+                | If eDP0 or DSI0 function                      |

|        |             |            |       |                         | is used, this pin will be no                  |

|        |             |            |       |                         | function.                                     |

| P118   | GPIO10      |            | S118  | LVDS1_2- / eDP1_TX2- /  | LVDS Only                                     |

|        |             |            |       | DSI1_D2-                | If eDP0 or DSI0 function                      |

|        |             |            |       |                         | is used, this pin will be no                  |

|        |             |            |       |                         | function.                                     |

| P119   | GPIO11      |            | S119  | GND                     |                                               |

| P120   | GND         |            | S120  | LVDS1_3+ / eDP1_TX3+ /  | LVDS Only                                     |

|        |             |            |       | DSI1_D3+                | If eDP0 or DSI0 function                      |

|        |             |            |       |                         | is used, this pin will be no                  |

| D.10.1 |             |            | 0.404 |                         | function                                      |

| P121   | I2C_PM_CK   |            | S121  | LVDS1_3- / eDP1_TX3- /  | LVDS Only                                     |

|        |             |            |       | DSI1_D3-                | If eDP0 or DSI0 function                      |

|        |             |            |       |                         | is used, this pin will be no function.        |

| P122   | ISC DM DAT  |            | S122  | LCD4 PKLT DWM           | Tunction.                                     |

|        | I2C_PM_DAT  | NO         |       | LCD1_BKLT_PWM           |                                               |

| P123   | BOOT_SEL0#  | NC         | S123  | GPIO13                  |                                               |

| P124   | BOOT_SEL1#  | NC         | S124  | GND                     |                                               |

| P125   | BOOT_SEL2#  |            | S125  | LVDS0_0+ / eDP0_TX0+ /  | Default LVDS, eDP or DSI                      |

|        |             |            |       | DSI0_D0+                | are option functions                          |

| P126   | RESET_OUT#  |            | S126  | LVDS0_0- / eDP0_TX0- /  | Default LVDS, eDP or DSI                      |

|        |             |            |       | DSI0_D0-                | are option functions                          |

| P127   | RESET_IN#   |            | S127  | LCD0_BKLT_EN            |                                               |

| P128   | POWER BTN#  |            | S128  | LVDS0_1+ / eDP0_TX1+ /  | Default LVDS, eDP or DSI                      |

|        | _           |            |       | DSI0_D1+                | are option functions                          |

| P129   | SER0_TX     |            | S129  | LVDS0_1- / eDP0_TX1- /  | Default LVDS, eDP or DSI                      |

| 20     | OLINO_TX    |            | 0.20  | DSI0_D1-                | are option functions                          |

| P130   | OFDO DV     |            | S130  | GND                     |                                               |

|        | SER0_RX     |            |       |                         | Default LVDC aDD as DCI                       |

| P131   | SER0_RTS#   |            | S131  | LVDS0_2+ / eDP0_TX2+ /  | Default LVDS, eDP or DSI are option functions |

|        |             |            |       | DSI0_D2+                | ·                                             |

| P132   | SER0_CTS#   |            | S132  | LVDS0_2- / eDP0_TX2- /  | Default LVDS, eDP or DSI                      |

|        |             |            |       | DSI0_D2-                | are option functions                          |

| P133   | GND         |            | S133  | LCD0_VDD_EN             |                                               |

| P134   | SER1_TX     |            | S134  | LVDS0_CK+ / eDP0_AUX+ / | Default LVDS, eDP or DSI                      |

|        |             |            |       | DSI0_CLK+               | are option functions                          |

| P135   | SER1_RX     |            | S135  | LVDS0_CK- / eDP0_AUX- / | Default LVDS, eDP or DSI                      |

|        |             |            |       | DSI0_CLK-               | are option functions                          |

|        |             |            | 1     |                         |                                               |

### 2.2 PCI Express

#### 2.2.1 PCle Groups

The Module *may* implement up to four PCle lanes. The links *may* be PCle Gen 1, 2 or 3, as the Module chip or chipset allows.

The Module PCIe links are primarily PCIe Root Complexes. If the chipset allows it, the PCIe link(s) *may* alternatively be configured as a PCIe target(s). This is Advantech specific.

Modules should implement the PCle Link A port. Modules may implement the PCle Links B, C and D ports. Fill order is A, B, C then D.

PCIe lanes C and D may implement SERDES alternatively.

PCI Express (or PCIe) is a scalable, point-to-point serial bus interface commonly used for high speed data exchange between a PCIe host, or root, and a target device. It is scalable in the sense that there may be link widths, per the PCIe specification, that are x1, x2, x4, x8, x16 or x32. SMARC currently calls out x1, x2 and x4 operation. Up to four PCIe x1 links may be implemented on a SMARC Module. There are three generations of PCIe defined, with each successive generation offering a speed increase, per the table below. The PCIe generation that may be supported on a particular SMARC Module is design and SOC dependent.

Table 4: PCIe Data Transfer Rates

| PCle       | Link Speed | Encoding /        | Net Data Transfer Rate |

|------------|------------|-------------------|------------------------|

| Generation | (x1 link)  | Overhead          |                        |

| 1          | 2.5 GT/s   | 8b/10b 20%        | 250 MB/s               |

| 2          | 5.0 GT/s   | 8b/10b 20%        | 500 MB/s               |

| 3          | 8.0 GT/s   | 128b / 130b 1.54% | 985 MB/s               |

PCI Express is defined in a series of documents maintained by the PCI Special Interest Group (www.pci-sig.org). The three most important documents to obtain are the Base Specification, the Card Electromechanical (CEM) Specification (which describes slot cards) and the Mini Card Electromechanical Specification (which describes the small format cards commonly referred to as Mini-PCIe cards).

#### 2.2.2 PCI Express Link Width

A connection between any two PCIe devices is known as a link, and is built up from a collection of one or more lanes. All devices *shall* support at least one single lane (x1) link. Devices may optionally support wider links composed of 2 or 4 lanes. Therefore the root complex *may* support different link width additionally to the x1 configuration.

The SMARC specification allows for multiple PCI Express link configurations. Check with Advantech which configurations are supported.

SMARC 2.11 adds CKREQ# signals for PCIe A and B to allow for enhanced power saving. The clock for PCIe D should be generated from the fixed clock of PCIe C.

Table 5: PCI Express Link Width

| SMARC<br>PCle Lane |                                        | Po                                     | ossible Link Configura      | ition                         |                              |

|--------------------|----------------------------------------|----------------------------------------|-----------------------------|-------------------------------|------------------------------|

| PCIe A             | x1                                     | x1                                     | 0                           | 0                             |                              |

| PCIe B             | x1                                     | x1                                     | x2                          | x2                            | x4                           |

| PCIe C             | x1                                     | x2                                     | x1                          | vo                            | Х4                           |

| PCIe D             | x1                                     | XZ                                     | x1                          | x2                            |                              |

| SMARC<br>PCle Lane |                                        | REF                                    | FCK and RST Assignr         | nents                         |                              |

| PCIe A             | PCIE_A_REFCK PCIE_A_CKREQ# PCIE_A_RST# | PCIE_A_REFCK PCIE_A_CKREQ# PCIE_A_RST# | PCIE_A_REFCK                | PCIE_A_REFCK                  |                              |

| PCle B             | PCIE_B_REFCK PCIE_B_CKREQ# PCIE_B_RST# | PCIE_B_REFCK PCIE_B_CKREQ# PCIE_B_RST# | PCIE_A_CKREQ# PCIE_A_RST#   | PCIE_A_CKREQ# PCIE_A_RST#     | PCIE_A_REFCK                 |

| PCle C             | PCIE_C_REFCK PCIE_C_RST#               |                                        | PCIE_B_REFCK                |                               | PCIE_A_CKREQ#<br>PCIE_A_RST# |

|                    | to be generated                        | PCIE_C_REFCK PCIE_C_RST#               | PCIE_B_CKREQ# PCIE_B_RST#   | PCIE_B_REFCK<br>PCIE_B_CKREQ# |                              |

| PCle D             | via buffer from<br>PCIe C signals      |                                        | PCIE_C_REFCK<br>PCIE_C_RST# | PCIE_B_RST#                   |                              |

### 2.2.3 General Purpose PCle Signal Definitions

Table 6: General Purpose PCI Express Signal Descriptions

| Signal        | Pin# | Description                                            | I/O     | Note |

|---------------|------|--------------------------------------------------------|---------|------|

| PCIE_A_RX+    | P86  | PCIe channel A. Receive Input differential pair.       | I PCIE  |      |

| PCIE_A_RX-    | P87  | Carrier Board:                                         | Runtime |      |

|               |      | Device - Connect AC Coupling cap 0.1/0.22uF near       |         |      |

|               |      | SMARC to PCIEA x1 device PETpA.                        |         |      |

|               |      | Slot - Connect to PCIEA x1 Conn pin A16, A17           |         |      |

|               |      | PERpA.                                                 |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_A_TX+    | P89  | PCIe channel A. Transmit Output differential pair.     | O PCIE  |      |

| PCIE_A_TX-    | P90  | Module has integrated AC Coupling Capacitor.           | Runtime |      |

|               |      | Carrier Board:                                         |         |      |

|               |      | Device - Connect to PCIEA x1 device PERpA.             |         |      |

|               |      | Slot - Connect to PCIEA x1 Conn pin B14, B15           |         |      |

|               |      | PETpA.                                                 |         |      |

|               |      | N/C if not used                                        |         |      |

| PCIE_A_REFCK+ | P83  | PCIe Reference Clock for PCIe lanes.                   | O PCIE  |      |

| PCIE_A_REFCK- | P84  | Carrier Board:                                         | Runtime |      |

|               |      | Connect 0Ω in series to                                |         |      |

|               |      | Device - PCIE device REFCLK+, REFCLK                   |         |      |

|               |      | Slot - PCIE Conn pin A13 REFCLK+, A14 REFCLK           |         |      |

|               |      | *Connect to PCIE Clock Buffer input to provide PCIE    |         |      |

|               |      | clocks output for more than one PCIE devices or slots. |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_A_RST#   | P75  | Reset output from Module to Carrier Board. Active      | 0       |      |

|               |      | low.                                                   | CMOS    |      |

|               |      | Module has integrated 3.3V buffer and series resistor. | Runtime |      |

|               |      | Connect to reset pin of devices except PCI slots or    | 3.3V    |      |

|               |      | devices.                                               |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_A_CKREQ# | P78  | PCIe Port A clock request.                             | IO OD   |      |

|               |      | Can be used for power saving mode on PCle - Pulled     | CMOS    |      |

|               |      | up or terminated on Module.                            | Runtime |      |

|               |      | N/C if not used.                                       | 3.3V    |      |

#### Embedded - IoT Pin# I/O Note Signal Description PCIE\_B\_RX+ I PCIE S87 PCIe channel B. Receive Input differential pair. PCIE B RX-Runtime **S88** Carrier Board: Device - Connect AC Coupling cap 0.1/0.22uF near SMARC to PCIEB x1 device PETpB. Slot - Connect to PCIEB x1 Conn pin A16, A17 PERpB. N/C if not used. PCIE\_B\_TX+ S90 PCIe channel A. Transmit Output differential pair. O PCIE PCIE B TX-Runtime S91 Module has integrated AC Coupling Capacitor. Carrier Board: Device - Connect to PCIEB x1 device PERpB. Slot - Connect to PCIEB x1 Conn pin B14, B15 PETpB. N/C if not used PCIe Reference Clock for PCIe lanes. O PCIE PCIE\_B\_REFCK+ S84 PCIE\_B\_REFCK-S85 Carrier Board: Runtime Connect $0\Omega$ in series to Device - PCIE device REFCLK+, REFCLK-. Slot - PCIE Conn pin A13 REFCLK+, A14 REFCLK-. \*Connect to PCIE Clock Buffer input to provide PCIE clocks output for more than one PCIE devices or slots. N/C if not used. PCIE\_B\_RST# S76 Reset output from Module to Carrier Board. Active low. O CMOS Module has integrated 3.3V buffer and series resistor. Runtime Connect to reset pin of devices except PCI slots or 3.3V devices. N/C if not used. PCIE B CKREQ# P77 PCIe Port A clock request. IO OD Can be used for power saving mode on PCIe - Pulled **CMOS** up or terminated on Module. Runtime N/C if not used. 3.3V I PCIE PCIE\_C\_RX+/ S78 PCIe channel C. Receive Input differential pair. SERDES\_1\_RX+ Runtime Carrier Board: Device - Connect AC Coupling cap 0.1uF near PCIE\_C\_RX-/ S79 SMARC to PCIEC x1 device PETpC. Slot - Connect to PCIEC x1 Conn pin A16, A17 SERDES\_1\_RX-PERpC. N/C if not used.

| Signal        | Pin# | Description                                            | I/O     | Note |

|---------------|------|--------------------------------------------------------|---------|------|

| PCIE_C_TX+/   | S81  | PCIe channel C. Transmit Output differential pair.     | O PCIE  |      |

| SERDES_1_TX+  |      | Module has integrated AC Coupling Capacitor.           | Runtime |      |

|               |      | Carrier Board:                                         |         |      |

| PCIE_C_TX-/   | S82  | Device - Connect to PCIEC x1 device PERpC.             |         |      |

| SERDES_1_TX-  |      | Slot - Connect to PCIEC x1 Conn pin B14, B15           |         |      |

|               |      | PETpC.                                                 |         |      |

|               |      | N/C if not used                                        |         |      |

| PCIE_C_REFCK+ | P80  | PCIe Reference Clock for PCIe lanes.                   | O PCIE  |      |

| PCIE_C_REFCK- | P81  | Carrier Board:                                         | Runtime |      |

|               |      | Connect $0\Omega$ in series to                         |         |      |

|               |      | Device - PCIE device REFCLK+, REFCLK                   |         |      |

|               |      | Slot - PCIE Conn pin A13 REFCLK+, A14 REFCLK           |         |      |

|               |      | *Connect to PCIE Clock Buffer input to provide PCIE    |         |      |

|               |      | clocks output for more than one PCIE devices or slots. |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_C_RST#   | S77  | Reset output from Module to Carrier Board. Active low. | O CMOS  |      |

|               |      | Module has integrated 3.3V buffer and series resistor. | Runtime |      |

|               |      | Connect to reset pin of devices except PCI slots or    | 3.3V    |      |

|               |      | devices.                                               |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_D_RX+/   | S32  | PCIe channel D. Receive Input differential pair.       | I PCIE  | 1    |

| SERDES_0_RX+  |      | Carrier Board:                                         | Runtime |      |

|               |      | Device - Connect AC Coupling cap 0.1/0.22uF near       |         |      |

| PCIE_D_RX-/   | S33  | SMARC to PCIED x1 device PETpD.                        |         |      |

| SERDES_0_RX-  |      | Slot - Connect to PCIED x1 Conn pin A16, A17           |         |      |

|               |      | PERpD.                                                 |         |      |

|               |      | N/C if not used.                                       |         |      |

| PCIE_D_TX+/   | S29  | PCIe channel C. Transmit Output differential pair.     | O PCIE  | 1    |

| SERDES_0_TX+  |      | Module has integrated AC Coupling Capacitor.           | Runtime |      |

|               |      | Carrier Board:                                         |         |      |

| PCIE_D_TX-/   | S30  | Device - Connect to PCIED x1 device PERpD.             |         |      |

| SERDES_0_TX-  |      | Slot - Connect to PCIED x1 Conn pin B14, B15           |         |      |

|               |      | PETpD.                                                 |         |      |

|               |      | N/C if not used                                        |         |      |

| Embedo     |      |                                                          |         |      |

|------------|------|----------------------------------------------------------|---------|------|

| Signal     | Pin# | Description                                              | I/O     | Note |

| PCIE_WAKE# | S146 | PCIe wake up interrupt to host – common to PCIe links    | IOD     |      |

|            |      | A, B, C, D – pulled up or terminated on Module           | CMOS    |      |

|            |      | This signal has 10K $\Omega$ pull up to 3.3V_DUAL on the | Standby |      |

|            |      | module.                                                  | 3.3V    |      |

|            |      | Device - Connect to WAKE# pin of PCIE device.            |         |      |

|            |      | Slot - Connect to WAKE# pin B11 of PCIE slot.            |         |      |

|            |      | Express Card - Connect to WAKE# pin 11 of Express        |         |      |

|            |      | Card socket.                                             |         |      |

|            |      | N/C if not used.                                         |         |      |

#### Note

1. SEDRES is option function.

#### 2.2.4 PCI Express\* General Routing Guidelines

#### 2.2.4.1 PCI Express Differential Transitional Via Recommendations

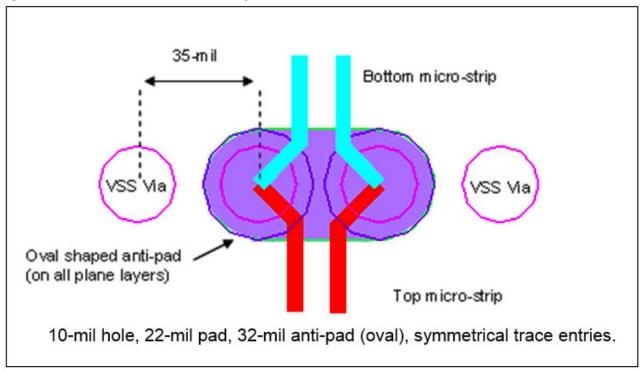

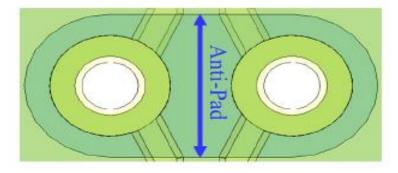

Transitional vias will use oval-shapes anti-pads on all plane layers. This can be created using a rectangular-shaped void to overlap with the usual round-shaped via anti-pad. The vias must also have a symmetrical trace entry.

Figure 2 and Table 7 provides the transitional differential via pad stack details.

Figure 1: Differential Transitional Via Layout

Table 7: Differential Transitional Via Layout Recommendations

| Parameter                     | Units | Recommendation |

|-------------------------------|-------|----------------|

| Via Diameter                  | mils  | 10             |

| Via Pad Size                  | mils  | 22             |

| Oval-Shaped Anti-Pad Size     | mils  | 32             |

| Via to via Distance(centered) | mils  | 35             |

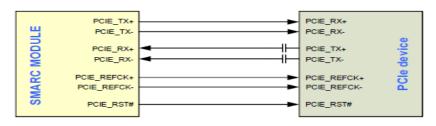

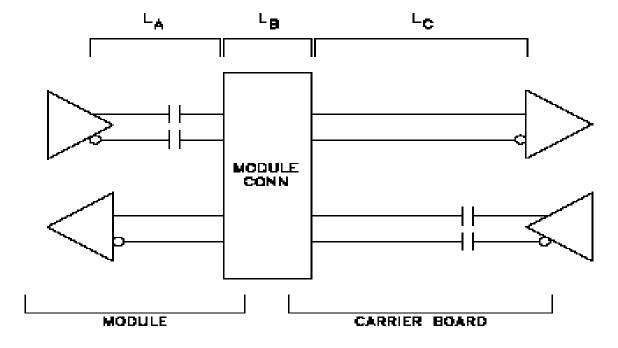

#### 2.2.4.2 PCle x1 Device Down on Carrier

An example of a PCIe x1 "device down" on the Carrier is shown below. Coupling caps on the SMARC PCIe TX and PCIe reference clock pairs are not needed on the Carrier. Coupling caps on the SMARC PCIe RX pair (TX pair from the Carrier PCIe device) are needed. They should be placed close to the Carrier device PCIe TX pins. Use 0402 package 0.2 or 0.1 uF X7R or X5R dielectric discrete ceramic capacitors. Do not use a capacitor array. Place the parts in a way to preserve the symmetry of the differential pair. Usually they are placed close to the Carrier device TX pins to avoid a via transition Figure 2: Interfacing a PCIe x1 Carrier Board Device

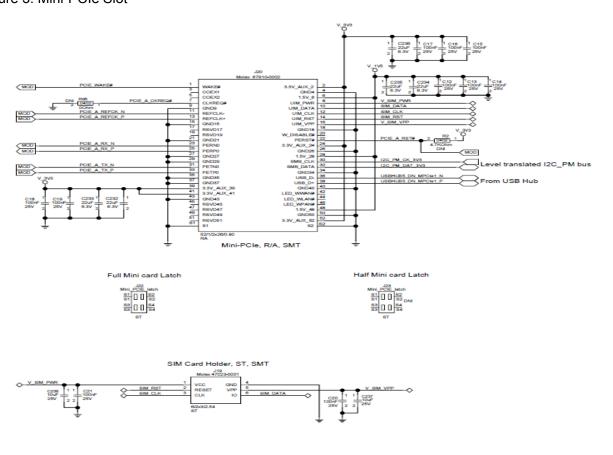

#### 2.2.4.3 Mini-PCle Slot

A SMARC Mini-PCIe implementation example is shown below. Mini-PCIe cards are defined to have pins for PCIe x1 and also a USB interface. A given card generally uses only one or the other. If you know exactly what Mini-PCIe card you plan to use, it is possible to omit either USB or PCIe. Generally, Mini-PCIe 802.11 WiFi cards use the PCIe interface and cellular modem cards use the USB interface. Figure 3: Mini-PCIe Slot

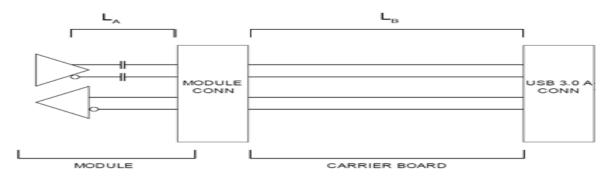

### 2.2.5 PCI Express\* Trace Length Guidelines

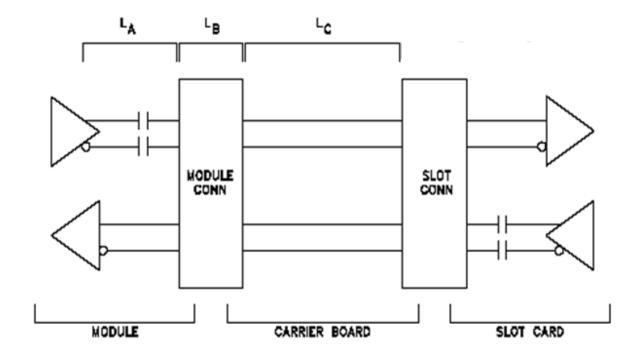

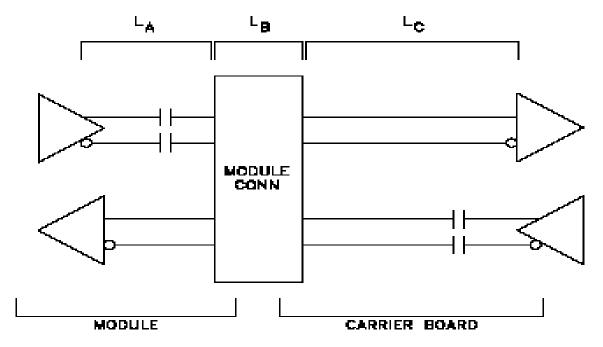

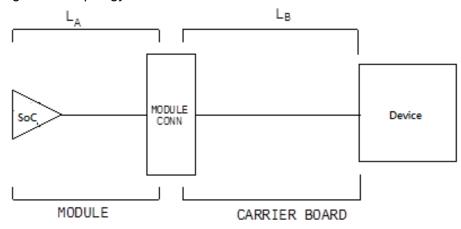

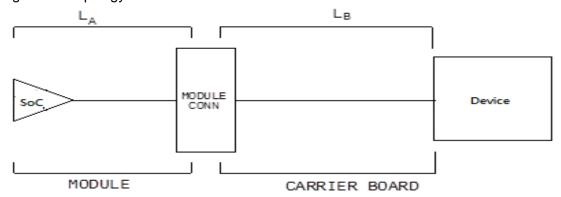

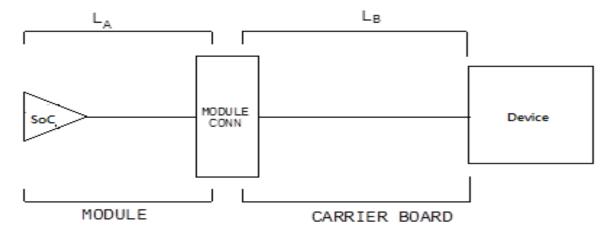

Figure 4: Topology for PCI Express Slot Card.

Figure 5: Topology for PCI Express Device Down.

Table 8: PCI Express Gen2\* Slot Card / Device Down Trace Length Guidelines

| Parameter                     | PCI Express Gen2                                      | Notes |

|-------------------------------|-------------------------------------------------------|-------|

| Symbol Rate / PCle Lane       | 5.0 G Symbols/s                                       |       |

| Differential Impedance Target | 85Ω±10%                                               |       |

| Single End                    | 50Ω±10%                                               |       |

| Spacing between differential  | Min. 50mils                                           |       |

| pairs and high-speed periodic |                                                       |       |

| signals                       |                                                       |       |

| Spacing between differential  | Min. 20mils                                           |       |

| pairs and low-speed non       |                                                       |       |

| periodic signals              |                                                       |       |

| Spacing between RX and TX     | Min. 20mils                                           |       |

| pairs (inter-pair) (s)        |                                                       |       |

| Spacing from edge of plane    | Min. 40mils                                           |       |

| LA + LB                       | Please see the SOM-2532 Layout Checklist              |       |

| Lc                            | Carrier Board Length                                  |       |

| Max length of LA+LB+LC        | Slot Card: 8.7"                                       |       |

|                               | Device Down: 10.5"                                    |       |

| Length matching               | Differential pairs (intra-pair): Max. ±2.5 mils       |       |

|                               | REFCLK+ and REFCLK- (intra-pair):Max. ±2.5mils        |       |

| Reference Plane               | GND referencing preferred                             |       |

|                               | Min 40-mil trace edge-to-major plane edge spacing     |       |

|                               | GND stitching vias required next to signal vias if    |       |

|                               | transitioning layers between GND layers               |       |

|                               | Power referencing acceptable if stitching caps are    |       |

|                               | used                                                  |       |

| Carrier Board Via Usage       | Max. 2 vias per TX trace, Max. 4 vias per RX trace    |       |

| AC coupling                   | The AC coupling capacitors for the TX lines are       | 1     |

|                               | incorporated on the SMARC Module. The AC coupling     |       |

|                               | capacitors for RX signal lines have to be implemented |       |

|                               | on the customer SMARC Carrier Board. Capacitor        |       |

|                               | type: X7R, 220nF ±10%, 16V, shape 0402.               |       |

#### Notes:

1. AC caps are recommended to be placed close to PCle device side (avoid placing AC caps on mid-bus).

Table 9: PCI Express Gen3 \* Slot Card / Device Down Trace Length Guidelines

| Parameter                     | PCI Express Gen3                                      | Notes |

|-------------------------------|-------------------------------------------------------|-------|

| Symbol Rate / PCle Lane       | 8.0 G Symbols/s                                       |       |

| Differential Impedance Target | 85Ω±10%                                               |       |

| Single End                    | 50Ω±10%                                               |       |

| Spacing between differential  | Min. 50mils                                           |       |

| pairs and high-speed periodic |                                                       |       |

| signals                       |                                                       |       |

| Spacing between differential  | Min. 20mils                                           |       |

| pairs and low-speed non       |                                                       |       |

| periodic signals              |                                                       |       |

| Spacing between RX and TX     | Min. 20mils                                           |       |

| pairs (inter-pair) (s)        |                                                       |       |

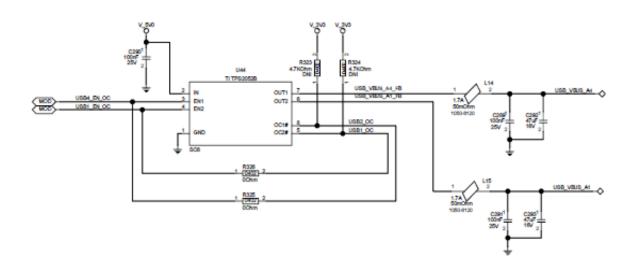

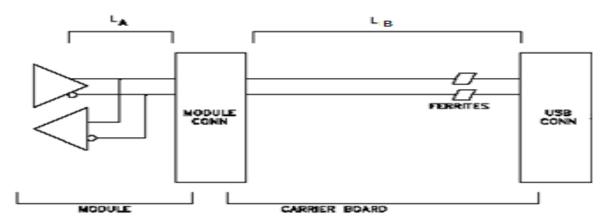

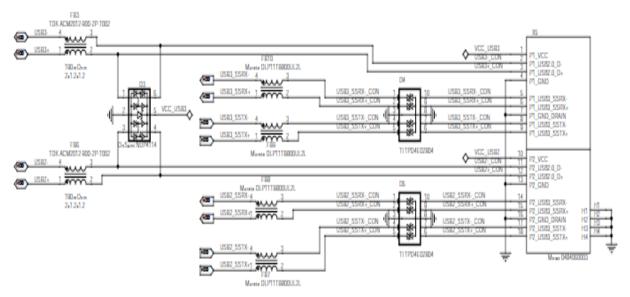

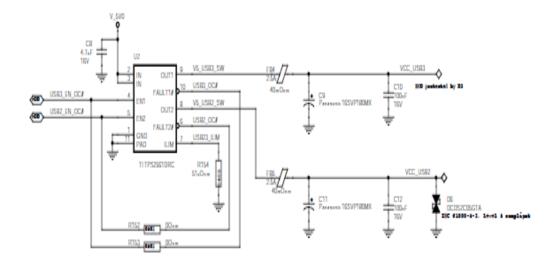

| Spacing from edge of plane    | Min. 40mils                                           |       |